GATE CSE Digital Logic Design PYQ

| Q1➡ | GATE 2021 set-1 Let the representation of a number in base 3 be 210. What is the hexadecimal representation of the number? |

| i ➥ 528 |

| ii ➥ D2 |

| iii ➥ 15 |

| iv ➥ 21 |

Show Answer With Best Explanation

Answer: III

Explanation:

Given,

(210)3

Calculation,

(210)3

First convert it into decimal represenation

= 2 x 32 + 1 x 31 + 0 x 30

= 2 x 9 + 3

= (21)10

now convert it into base 2 representation

= (10101)2

now make a pair of 4 bits and then convert 4 bits into decimal representation to get hexadecimal representation because log216 = 4 bits

=(0001 0101)2

= (15)16

So, Option(II) is correct.

| More Discussion | Explanation On YouTube | Number System | Help-Line |

| Q2➡ | GATE 2021 set-1 Consider the following representation of a number in IEEE 754 single-precision floating point format with a bias of 127. S : 1 E : 10000001 F : 11110000000000000000000 Here S, E and F denote the sign, exponent and fraction components of the floating point representation. The decimal value corresponding to the above representation (rounded to 2 decimal places) is _________. |

Show Answer With Best Explanation

Answer: -7.75

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Number System | Help-Line |

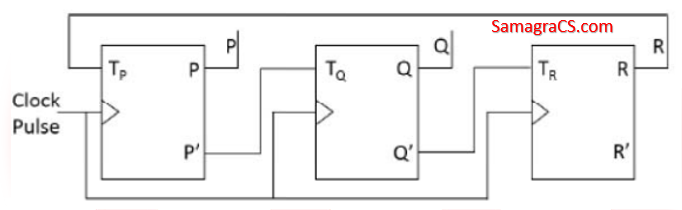

| Q3➡ | GATE 2021 set-1 Consider a 3-bit counter, designed using T flip-flops, as shown below:  Assuming the initial state of the counter given by PQR as 000, what are the next three states? |

| i ➥ 011, 101, 111 |

| ii ➥ 001, 010, 000 |

| iii ➥ 001, 010, 111 |

| iv ➥ 011, 101, 000 |

Show Answer With Best Explanation

Answer: IV

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Sequential Circuits | Help-Line |

| Q4➡ | GATE 2021 set-1 Which one of the following choices gives the correct values of x and y? |

| i ➥ x is 1 and y is 0 |

| ii ➥ x is 0 and y is 0 |

| iii ➥ x is 0 and y is 1 |

| iv ➥ x is 1 and y is 1 |

Show Answer With Best Explanation

Answer: II

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Number Systems | Help-Line |

| Q5➡ | GATE 2021 set-1 |

| i ➥ |

| ii ➥ |

| iii ➥ |

| iv ➥ |

Show Answer With Best Explanation

Answer: i,iii,iv

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Boolean Function | Help-Line |

| Q6➡ | GATE 2021 set-2 Which one of the following circuits implements the Boolean function given below? f(x,y,z) = m0 + m1 + m3 + m4 + m5 +m6 , where mi is the ith minterm. |

| i ➥ |

| ii ➥ |

| iii ➥ |

| iv ➥ |

Show Answer With Best Explanation

Answer: I

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Combinational Circuits | Help-Line |

| Q7➡ | GATE 2021 set-2 The format of the single-precision floating-point representation of a real number as per the IEEE 754 standard is as follows: Which one of the following choices is correct with respect to the smallest normalized positive number represented using the standard? |

| i ➥ exponent = 00000001 and mantissa = 00000000000000000000001 |

| ii ➥ exponent = 00000000 and mantissa = 00000000000000000000000 |

| iii ➥ exponent = 00000000 and mantissa = 00000000000000000000001 |

| iv ➥ exponent = 00000001 and mantissa = 00000000000000000000000 |

Show Answer With Best Explanation

Answer: IV

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Number System | Help-Line |

| Q8➡ | GATE 2021 set-2 If x and y are two decimal digits and (0.1101)2=(0.8xy5)10, the decimal value of x+y is _____. |

Show Answer With Best Explanation

Answer: 3

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Number System | Help-Line |

| Q9➡ | GATE 2021 set-2 If the numerical value of a 2-byte unsigned integer on a little endian computer is 255 more than that on a big endian computer, which of the following choices represent(s) the unsigned integer on a little endian computer? |

| i ➥ 0x0100 |

| ii ➥ 0x6665 |

| iii ➥ 0x4243 |

| iv ➥ 0x0001 |

Show Answer With Best Explanation

Answer: I, II

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Number System | Help-Line |

| Q10➡ | GATE 2021 set-2 Consider a Boolean function f(w, x, y, z) such that f(w, 0, 0, z) = 1 f(1, x, 1, z) = x + z f(w, 1, y, z) = wz + y The number of literals in the minimal sum-of-products expression of f is _______. |

Show Answer With Best Explanation

Answer: 6

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Boolean Algebra | Help-Line |

| Q11➡ | GATE 2020 If there are m input lines and n output lines for a decoder that is used to uniquely address a byte addressable 1 KB RAM, then the minimum value of m + n is ______. |

Show Answer With Best Explanation

Answer: 1034

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Combinational Circuit | Help-Line |

| Q12➡ | GATE 2020 A multiplexer is placed between a group of 32 registers and an accumulator to regulate data movement such that at any given point in time the content of only one register will move to the accumulator. The minimum number of select lines needed for the multiplexer is _______. |

Show Answer With Best Explanation

Answer: 5

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Combinational Circuit | Help-Line |

| Q13➡ | GATE 2020 Consider three registers R1, R2 and R3 that store numbers in IEEE-754 single precision floating point format. Assume that R1 and R2 contain the values (in hexadecimal notation) 0x42200000 and 0xC1200000, respectively. If R3 = R1/R2, what is the value stored in R3? |

| i ➥ 0x83400000 |

| ii ➥ 0xC8500000 |

| iii ➥ 0xC0800000 |

| iv ➥ 0x40800000 |

Show Answer With Best Explanation

Answer: III

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Number System | Help-Line |

| Q14➡ | GATE 2020 Consider the Boolean function z(a,b,c) Which one of the following minterm lists represents the circuit given above ? |

| i ➥ Z = ∑(2,3,5) |

| ii ➥ Z = ∑(0,1,3,7) |

| iii ➥ Z = ∑(1,4,5,6,7). |

| iv ➥ Z = ∑(2,4,5,6,7). |

Show Answer With Best Explanation

Answer: III

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Boolean Algebra | Help-Line |

| Q15➡ | GATE 2019 Which one of the following is NOT a valid identity? |

| i ➥ x ⊕ y = x + y, if xy = 0 |

| ii ➥ (x ⊕ y) ⊕ z = x ⊕ (y ⊕ z) |

| iii ➥ x ⊕ y = (xy + x’y’)’ |

| iv ➥ (x + y) ⊕ z = x ⊕ (y + z) |

Show Answer With Best Explanation

Answer: IV

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Boolean Algebra | Help-Line |

| Q16➡ | GATE 2019 In 16-bit 2’s complement representation, the decimal number -28 is: |

| i ➥ 1000 0000 1110 0100 |

| ii ➥ 1111 1111 1110 0100 |

| iii ➥ 1111 1111 0001 1100 |

| iv ➥ 0000 0000 1110 0100 |

Show Answer With Best Explanation

Answer: II

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Number System | Help-Line |

| Q17➡ | GATE 2019 Two numbers are chosen independently and uniformly at random from the set {1, 2, …, 13}. The probability (rounded off to 3 decimal places) that their 4-bit (unsigned) binary representations have the same most significant bit is ________. |

Show Answer With Best Explanation

Answer: 0.502 to 0.504

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Number System | Help-Line |

| Q18➡ | GATE 2019 Consider three 4-variable functions f1, f2 and f3, which are expressed in sum-of-minterms as f1 = Σ(0, 2, 5, 8, 14), f2 = Σ(2, 3, 6, 8, 14, 15), f3 = Σ(2, 7, 11, 14) For the following circuit with one AND gate and one XOR gate, the output function f can be expressed as: |

| i ➥ Σ (0, 2, 3, 5, 6, 7, 8, 11, 14, 15) |

| ii ➥ Σ (7, 8, 11) |

| iii ➥ Σ (2, 14) |

| iv ➥ Σ (2, 7, 8, 11, 14) |

Show Answer With Best Explanation

Answer: II

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Boolean Algebra | Help-Line |

| Q19➡ | GATE 2019 What is the minimum number of 2-input NOR gates required to implement a 4-variable function function expressed in sum-of-minterms form as f = Σ(0, 2, 5, 7, 8, 10, 13, 15)? Assume that all the inputs and their complements are available. |

Show Answer With Best Explanation

Answer: 3

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Boolean Algebra | Help-Line |

| Q20➡ | GATE 2018 Let ⊕ and ⊙ denote the Exclusive OR and Exclusive NOR operations, respectively. Which one of the following is NOT CORRECT? |

| i ➥ |

| ii ➥ |

| iii ➥ |

| iv ➥ |

Show Answer With Best Explanation

Answer: I

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Boolean Algebra | Help-Line |

| Q21➡ | GATE 2018 Consider the sequential circuit shown in the figure, where both flip-flops used are positive edge-triggered D flip-flops. The number of states in the state transition diagram of this circuit that have a transition back to the same state on some value of “in” is _____. |

Show Answer With Best Explanation

Answer: 2

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Sequential Circuits | Help-Line |

| Q22➡ | GATE 2018 Consider the unsigned 8-bit fixed point binary number representation below. b7 b6 b5 b4 b3 . b2 b1 b0 where the position of the binary point is between b3 and b2 . Assume b7 is the most significant bit. Some of the decimal numbers listed below cannot be represented exactly in the above representation: (i) 31.500 (ii) 0.875 (iii) 12.100 (iv) 3.001 Which one of the following statements is true? |

| i ➥ None of (i), (ii), (iii), (iv) can be exactly represented |

| ii ➥ Only (ii) cannot be exactly represented |

| iii ➥ Only (iii) and (iv) cannot be exactly represented |

| iv ➥ Only (i) and (ii) cannot be exactly represented |

Show Answer With Best Explanation

Answer: III

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Number System | Help-Line |

| Q23➡ | GATE 2018 Consider the minterm list form of a Boolean function F given below. Here, m denotes a minterm and d denotes a don’t care term. The number of essential prime implicants of the function F is _______. |

Show Answer With Best Explanation

Answer: 3

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Boolean Algebra | Help-Line |

| Q24➡ | GATE 2017 Set-1 When two 8-bit numbers A7…A0 and B7…B0 in 2’s complement representation (with A0 and B0 as the least significant bits) are added using a ripple-carry adder, the sum bits obtained are S7…S0 and the carry bits are C7…C0. An overflow is said to have occurred if |

| i ➥ (A7 . B7 . S7‘ + A7‘. B7‘. S7) is 1 |

| ii ➥ the carry bit C7 is 1 |

| iii ➥ (A0 . B0 . S0‘ + A0‘. B0‘. S0) is 1 |

| iv ➥ all the carry bits (C7,…,C0) are 1 |

Show Answer With Best Explanation

Answer: I

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Number System | Help-Line |

| Q25➡ | GATE 2017 Set-1 The n-bit fixed-point representation of an unsigned real number X uses f bits for the fraction part. Let i = n-f. The range of decimal values for X in this representation is |

| i ➥ 0 to 2i |

| ii ➥ 0 to (2i – 2-f ) |

| iii ➥ 2-f to 2i |

| iv ➥ 2-f to (2i – 2-f) |

Show Answer With Best Explanation

Answer: II

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Number System | Help-Line |

| Q26➡ | GATE 2017 Set-1 Consider the Karnaugh map given below, where X represents “don’t care” and blank represents 0. Assume for all inputs (a, b, c, d) , the respective complements (a’, b’, c’, d’) are also available. The above logic is implemented using 2-input NOR gates only. The minimum number of gates required is ___________. |

Show Answer With Best Explanation

Answer: 1.0

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Boolean Algebra | Help-Line |

| Q27➡ | GATE 2017 Set-1 Consider a combination of T and D flip-flops connected as shown below. The output of the D flip-flop is connected to the input of the T flip-flop and the output of the T flip-flop is connected to the input of the D flip-flop: Initially, both Q0 and Q1 are set to 1 (before the 1st clock cycle). The outputs |

| i ➥ Q1Q0 after the 3rd cycle are 00 and after the 4th cycle are 11 respectively |

| ii ➥ Q1Q0 after the 3rd cycle are 11 and after the 4th cycle are 00 respectively |

| iii ➥ Q1Q0 after the 3rd cycle are 01 and after the 4th cycle are 01 respectively |

| iv ➥ Q1Q0 after the 3rd cycle are 11 and after the 4th cycle are 01 respectively |

Show Answer With Best Explanation

Answer: IV

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Sequential Circuits | Help-Line |

| Q28➡ | GATE 2017 Set-2 The representation of the value of a 16-bit unsigned integer X in hexadecimal number system is BCA9. The representation of the value of X in octal number system is: |

| i ➥ 136252 |

| ii ➥ 571247 |

| iii ➥ 736251 |

| iv ➥ 136251 |

Show Answer With Best Explanation

Answer: IV

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Number System | Help-Line |

| Q29➡ | GATE 2017 Set-2 Given the following binary number in 32-bit (single precision) IEEE-754 format: 00111110011011010000000000000000 The decimal value closest to this floating-point number is |

| i ➥ 2.27 × 10-1 |

| ii ➥ 1.45 × 101 |

| iii ➥ 1.45 × 10-1 |

| iv ➥ 2.27 × 101 |

Show Answer With Best Explanation

Answer: I

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Number System | Help-Line |

| Q30➡ | GATE 2017 Set-2 Consider a quadratic equation x2 – 13x + 36 = 0 with coefficients in a base b. The solutions of this equation in the same base b are x = 5 and x = 6. Then b=_________. |

Show Answer With Best Explanation

Answer: 8

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Number System | Help-Line |

| Q31➡ | GATE 2017 Set-2 Given f(w,x,y,z) = Σm(0,1,2,3,7,8,10) + Σd(5,6,11,15), where d represents the don’t-care condition in Karnaugh maps. Which of the following is a minimum product-of-sums (POS) form of f(w,x,y,z)? |

| i ➥ f = (w’ + z’) (x’ + z) |

| ii ➥ f = (w’ + z) (x + z) |

| iii ➥ f = (w + z) (x’ + z) |

| iv ➥ f = (w + z’) (x’ + z) |

Show Answer With Best Explanation

Answer: I

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Boolean Algebra | Help-Line |

| Q32➡ | GATE 2017 Set-2 If w, x, y, z are Boolean variables, then which one of the following is INCORRECT? |

| i ➥ wx + w(x + y) + x(x + y) = x + wy |

| ii ➥ |

| iii ➥ |

| iv ➥ (w + y)(wxy + wyz) = wxy + wyz |

Show Answer With Best Explanation

Answer: III

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Boolean Algebra | Help-Line |

| Q33➡ | GATE 2017 Set-2 Consider a binary code that consists of only four valid code words as given below: 00000, 01011, 10101, 11110 Let the minimum Hamming distance of the code be p and the maximum number of erroneous bits that can be corrected by the code be q. Then the values of p and q are |

| i ➥ p=4 and q=2 |

| ii ➥ p=4 and q=1 |

| iii ➥ p=3 and q=2 |

| iv ➥ p=3 and q=1 |

Show Answer With Best Explanation

Answer: IV

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Number System | Help-Line |

| Q38➡ | GATE 2017 Set-2 The next state table of a 2-bit saturating up-counter is given below. The counter is built as a synchronous sequential circuit using T flip-flops. The expressions for T1 and T0 are |

| i ➥ T1=Q1Q0 , T0 = Q’1Q’0 |

| ii ➥ T1=Q’1Q0 , T0 = Q’1 + Q’0 |

| iii ➥ T1=Q1 + Q0 , T0 = Q’1 + Q’0 |

| iv ➥ T1=Q’1Q0 , T0 = Q1 + Q0 |

Show Answer With Best Explanation

Answer: II

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Sequential Circuits | Help-Line |

| Q39➡ | GATE 2016 Set-1 Consider the Boolean operator with the following properties: x # 0 = x , x # 1 = x’ , x # x = 0 , x # x’ = 1 Then x#y is equivalent to |

| i ➥ xy’ + x’y |

| ii ➥ xy’ + x’y’ |

| iii ➥ x’y + xy |

| iv ➥ xy + x’y’ |

Show Answer With Best Explanation

Answer: I

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Boolean Algebra | Help-Line |

| Q40➡ | GATE 2016 Set-1 The 16-bit 2’s complement representation of an integer is 1111 1111 1111 0101; its decimal representation is ___________. |

Show Answer With Best Explanation

Answer: -11

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Number Systems | Help-Line |

| Q41➡ | GATE 2016 Set-1 We want to design a synchronous counter that counts the sequence 0-1-0-2-0-3 and then repeats. The minimum number of J-K flip-flops required to implement this counter is _________. |

Show Answer With Best Explanation

Answer: 4

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Sequential Circuits | Help-Line |

| Q42➡ | GATE 2016 Set-1 Consider the two cascaded 2-to-1 multiplexers as shown in the figure. The minimal sum of products form of the output X is |

| i ➥ P’Q’ + PQR |

| ii ➥ P’Q + QR |

| iii ➥ PQ + P’Q’R |

| iv ➥ Q’R’ + PQR |

Show Answer With Best Explanation

Answer: IV

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Combinational Circuits | Help-Line |

| Q43➡ | GATE 2016 Set-1 Consider a carry lookahead adder for adding two n-bit integers, built using gates of fan-in at most two. The time to perform addition using this adder is __________. |

| i ➥ Θ(1) |

| ii ➥ Θ(log(n)) |

| iii ➥ Θ(√n) |

| iv ➥ Θ(n) |

Show Answer With Best Explanation

Answer: II

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Combinational Circuits | Help-Line |

| Q44➡ | GATE 2016 Set-2 Consider an eight-bit ripple-carry adder for computing the sum of A and B, where A and B are integers represented in 2’s complement form. If the decimal value of A is one, the decimal value of B that leads to the longest latency for the sum to stabilize is ________. |

Show Answer With Best Explanation

Answer: -11

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Combinational Circuits | Help-Line |

| Q45➡ | GATE 2016 Set-2 Let, x1⊕x2⊕x3⊕x4 = 0 where x1, x2, x3, x4 are Boolean variables, and ⊕ is the XOR operator. Which one of the following must always be TRUE? |

| i ➥ x1x2x3x4 = 0 |

| ii ➥ x1x3+x2 = 0 |

| iii ➥ x1‘⊕x3‘ = x2‘⊕x4‘ |

| iv ➥ x1 + x2 + x3 + x4 = 0 |

Show Answer With Best Explanation

Answer: III

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Boolean Algebra | Help-Line |

| Q46➡ | |