GATE 2011 CSE Computer Science and information technology

[Q1 – Q25 carry ONE mark each ]

| Q1➡ | Compiler Design In a compiler, keywords of a language are recognized during |

| i ➥ Parsing of the program |

| ii ➥ The code generation |

| iii ➥ The lexical analysis of the program |

| iv ➥ Dataflow analysis |

Show Answer With Best Explanation

Answer: III

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Compiler Phases | Help-Line |

| Q2➡ | Computer Network A layer-4 firewall (a device that can look at all protocol headers up to the transport layer) CANNOT |

| i ➥ block entire HTTP traffic during 9:00PM and 5:00AM |

| ii ➥ block all ICMP traffic |

| iii ➥ stop incoming traffic from a specific IP address but allow outgoing traffic to the same IP address |

| iv ➥ block TCP traffic from a specific user on a multi-user system during 9:00PM and 5:00AM |

Show Answer With Best Explanation

Answer: IV

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Firewall | Help-Line |

| Q3➡ | Engineering Mathematics If two fair coins are flipped and at least one of the outcomes is known to be a head, what is the probability that both outcomes are heads? |

| i ➥ 1/3 |

| ii ➥ 1/4 |

| iii ➥ 1/2 |

| iv ➥ 2/3 |

Show Answer With Best Explanation

Answer: I

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Probability | Help-Line |

| Q4➡ | Computer Network Consider different activities related to email: m1: Send an email from a mail client to a mail server m2: Download an email from mailbox server to a mail client m3: Checking email in a web browser Which is the application level protocol used in each activity? |

| i ➥ m1: HTTP m2: SMTP m3: POP |

| ii ➥ m1: SMTP m2: FTP m3: HTTP |

| iii ➥ m1: SMTP m2: POP m3: HTTP |

| iv ➥ m1: POP m2: SMTP m3: IMAP |

Show Answer With Best Explanation

Answer: III

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Application Layer Protocol | Help-Line |

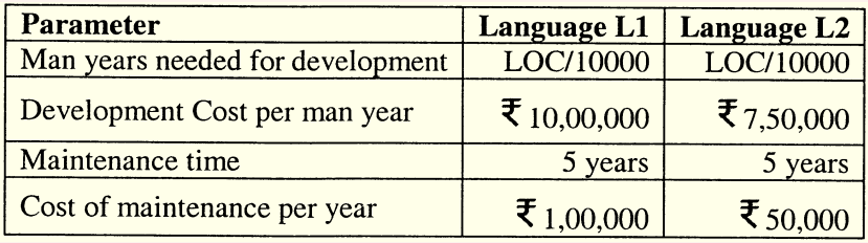

| Q5➡ | Software Engineering A company needs to develop a strategy for software product development for which it has a choice of two programming languages L1 and L2. The number of lines of code (LOC) developed using L2 is estimated to be twice the LOC developed with Ll. The product will have to be maintained for five years. Various parameters for the company are given in the table below.  Total cost of the project includes cost of development and maintenance. What is the LOC for L1 for which the cost of the project using L1 is equal to the cost of the project using L2? |

| i ➥ 4000 |

| ii ➥ 5000 |

| iii ➥ 4333 |

| iv ➥ 4667 |

Show Answer With Best Explanation

Answer: II

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | LOC | Help-Line |

| Q6➡ | Operating Systems Let the time taken to switch between user and kernel modes of execution be t1 while the time taken to switch between two processes be t2. Which of the following is TRUE? |

| i ➥ (t1) > (t2) |

| ii ➥ (t1) = (t2) |

| iii ➥ (t1) < (t2) |

| iv ➥ Nothing can be said about the relation between t1 and t2 |

Show Answer With Best Explanation

Answer: III

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Context Switching | Help-Line |

| Q7➡ | Software Engineering A company needs to develop digital signal processing software for one of its newest inventions. The software is expected to have 40000 lines of code. The company needs to determine the effort in person-months needed to develop this software using the basic COCOMO model. The multiplicative factor for this model is given as 2.8 for the software development on embedded systems, while the exponentiation factor is given as 1.20. What is the estimated effort in person-months? |

| i ➥ 234.25 |

| ii ➥ 932.50 |

| iii ➥ 287.80 |

| iv ➥ 122.40 |

Show Answer With Best Explanation

Answer: I

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | COCOMO Model | Help-Line |

| Q8➡ | Theory of Computation Which of the following pairs have DIFFERENT expressive power? |

| i ➥ Deterministic finite automata (DFA) and Non-deterministic finite automata (NFA) |

| ii ➥ Deterministic push down automata (DPDA) and Non-deterministic push down automata (NPDA) |

| iii ➥ Deterministic single-tape Turning machine and Non-deterministic single tape Turning machine |

| iv ➥ Single-tape Turning machine and multi-tape Turning machine |

Show Answer With Best Explanation

Answer: II

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Expressive Power | Help-Line |

| Q9➡ | HTML HTML (Hyper Text Markup Language) has language elements which permit certain actions other than describing the structure of the web document. Which one of the following actions is NOT supported by pure HTML (without any server or client side scripting) pages? |

| i ➥ Embed web objects from different sites into the same page |

| ii ➥ Refresh the page automatically after a specified interval |

| iii ➥ Automatically redirect to another page upon download |

| iv ➥ Display the client time as part of the page |

Show Answer With Best Explanation

Answer: IV

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | HTML | Help-Line |

| Q10➡ | Software Engineering Which of the following is NOT desired in a good Software Requirement Specifications (SRS) document? |

| i ➥ Functional Requirements |

| ii ➥ Non-Functional Requirements |

| iii ➥ Goals of Implementation |

| iv ➥ Algorithms for Software Implementation |

Show Answer With Best Explanation

Answer: IV

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | SRS | Help-Line |

| Q11➡ | Computer Organization A computer handles several interrupt sources of which the following are relevant for this question. . Interrupt from CPU temperature sensor (raises interrupt if CPU temperature is too high) . Interrupt from Mouse(raises interrupt if the mouse is moved or a button is pressed) . Interrupt from Keyboard(raises interrupt when a key is pressed or released) . Interrupt from Hard Disk(raises interrupt when a disk read is completed) Which one of these will be handled at the HIGHEST priority? |

| i ➥ Interrupt from Hard Dist |

| ii ➥ Interrupt from Mouse |

| iii ➥ Interrupt from Keyboard |

| iv ➥ Interrupt from CPU temperature sensor |

Show Answer With Best Explanation

Answer: IV

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Interrupt | Help-Line |

| Q12➡ | Database Management System Consider a relational table with a single record for each registered student with the following attributes. Registration_Num: Unique registration number of each registered student UID: Unique identity number, unique at the national level for each citizen BankAccount_Num: Unique account number at the bank. A student can have multiple accounts or join accounts. This attribute stores the primary account number. Name: Name of the student Hostel_Room: Room number of the hostel Which one of the following option is INCORRECT? |

| i ➥ BankAccount_Num is a candidate key |

| ii ➥ Registration_Num can be a primary key |

| iii ➥ UID is a candidate key if all students are from the same country |

| iv ➥ If S is a superkey such that S∩UID is NULL then S∪UID is also a superkey |

Show Answer With Best Explanation

Answer: I

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Keys | Help-Line |

| Q13➡ | Digital Logic Design Which one of the following circuits is NOT equivalent to a 2-input XNOR (exclusive NOR) gate? |

| i ➥ |

| ii ➥ |

| iii ➥ |

| iv ➥ |

Show Answer With Best Explanation

Answer: IV

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Logic Gates | Help-Line |

| Q14➡ | Digital Logic Design The simplified SOP (sum of product) form of the boolean expression (P + Q’ + R’) . (P + Q’ +R) . (P + Q + R’) |

| i ➥ (P’.Q + R’) |

| ii ➥ (P+Q’.R’) |

| iii ➥ (P’.Q + R) |

| iv ➥ (P.Q + R) |

Show Answer With Best Explanation

Answer: II

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Boolean Expression | Help-Line |

| Q15➡ | Digital Logic Design The minimum number of D flip-flops needed to design a mod-258 counter is |

| i ➥ 9 |

| ii ➥ 8 |

| iii ➥ 512 |

| iv ➥ 258 |

Show Answer With Best Explanation

Answer: I

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Sequential Circuits | Help-Line |

| Q16➡ | Operating Systems A thread is usually defined as a “light weight process” because an operating system (OS) maintains smaller data structures for a thread than for a process. In relation to this, which of the following is TRUE? |

| i ➥ On per-thread basis, the OS maintains only CPU register state |

| ii ➥ The OS does not maintain a separate stack for each thread |

| iii ➥ On per-thread basis, the OS does not maintain virtual memory state |

| iv ➥ On per thread basis, the OS maintains only scheduling and accounting information |

Show Answer With Best Explanation

Answer: III

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Threads | Help-Line |

| Q17➡ | Engineering Mathematics K4 and Q3 are graphs with the following structures. Which one of the following statement is TRUE in relation to these graphs? |

| i ➥ K4 is planar while Q3 is not |

| ii ➥ Both K4 and Q3 are planar |

| iii ➥ Q3 is planar while K4 is not |

| iv ➥ Neither K4 not Q3 is planar |

Show Answer With Best Explanation

Answer: II

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Graph Theory | Help-Line |

| Q18➡ | Engineering Mathematics If the difference between the expectation of the square of a random variable (E[X2]) and the square of the expectation of the random variable (E[X])2 is denoted by R, then |

| i ➥ R = 0 |

| ii ➥ R < 0 |

| iii ➥ R ≥ 0 |

| iv ➥ R > 0 |

Show Answer With Best Explanation

Answer: III

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Probability | Help-Line |

| Q19➡ | Compiler Design The lexical analysis for a modern computer language such as Java needs the power of which one of the following machine models in a necessary and sufficient sense? |

| i ➥ Finite state automata |

| ii ➥ Deterministic pushdown automata |

| iii ➥ Non-Deterministic pushdown automata |

| iv ➥ Turing machine |

Show Answer With Best Explanation

Answer: I

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Compilers | Help-Line |

| Q20➡ | Operating Systems Let the page fault service time to 10 ms in a computer with average memory access time being 20 ns. If one page fault is generated for every 106 memory accesses, what is the effective access time for the memory? |

| i ➥ 21 ns |

| ii ➥ 30 ns |

| iii ➥ 23 ns |

| iv ➥ 35 ns |

Show Answer With Best Explanation

Answer: II

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Memory Management | Help-Line |

| Q21➡ | Computer Organization Consider a hypothetical processor with an instruction of type LW R1, 20 (R2), which during execution reads a 32-bit word from memory and stores it in a 32-bit register R1. The effective address of the memory location is obtained by the addition of constant 20 and the contents of register R2. Which of the following best reflects the addressing mode implemented by this instruction for the operand memory? |

| i ➥ Immediate Addressing |

| ii ➥ Register Addressing |

| iii ➥ Register Indirect Scaled Addressing |

| iv ➥ Base Indexed Addressing |

Show Answer With Best Explanation

Answer: IV

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Machine Instructions | Help-Line |

| Q22➡ | Programming What does the following fragment of C-program print? |

| i ➥ GATE2011 |

| ii ➥ E2011 |

| iii ➥ 2011 |

| iv ➥ 011 |

Show Answer With Best Explanation

Answer: III

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Program | Help-Line |

| Q23➡ | Data Structures A max-heap is a heap where the value of each parent is greater than or equal to the value of its children. Which of the following is a max-heap? |

| i ➥ |

| ii ➥ |

| iii ➥ |

| iv ➥ |

Show Answer With Best Explanation

Answer: II

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Heap Tree | Help-Line |

| Q24➡ | Theory of Computation Let P be a regular language and Q be a context-free language such that Q ⊆ P. (For example, let P be the language represented by the regular expression p*q* and Q be [pnqn | n ∈ N]). Then which of the following is ALWAYS regular? |

| i ➥ P ∩ Q |

| ii ➥ P – Q |

| iii ➥ Σ* – P |

| iv ➥ Σ* – Q |

Show Answer With Best Explanation

Answer: III

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Regular Language | Help-Line |

| Q25➡ | Theory of Computation An algorithm to find the length of the longest monotonically increasing sequence of numbers in an array A[0:n-1] is given below. Let Li denote the length of the longest monotonically increasing sequence starting at index i in the array Initialize Ln-1=1. For all i such that 0≤i≤n-2 Finally the length of the longest monotonically increasing sequence is Max(L0, L1, …, Ln-1). Which of the following statements is TRUE? |

| i ➥ The algorithm uses dynamic programming paradigm |

| ii ➥ The algorithm has a linear complexity and uses branch and bound paradigm |

| iii ➥ The algorithm has a non-linear polynomial complexity and uses branch and bound paradigm |

| iv ➥ The algorithm uses divide and conquer paradigm |

Show Answer With Best Explanation

Answer: I

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Dynamic Programming | Help-Line |

[Q26 – Q55 carry TWO mark each ]

| Q26➡ | Theory of Computation Consider the languages L1,L2 and L3 as given below. L1 = {0p1q | p,q∈N}, L2 = {0p1q | p,q∈N and p=q} and L3 = {0p1q0r | p,q,r∈N and p=q=r}. Which of the following statements is NOT TRUE? |

| i ➥ Push Down Automate (PDA) can be used to recognize L1 and L2 |

| ii ➥ L1 is a regular language |

| iii ➥ All the three languages are context free |

| iv ➥ Turing machines can be used to recognize all the languages |

Show Answer With Best Explanation

Answer: III

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Language | Help-Line |

| Q27➡ | Compiler Design Consider two binary operators ‘↑’ and ‘↓’ with the precedence of operator ↓ being lower than that of the operator ↑. Operator ↑ is right associative while operator ↓, is left associative. Which one of the following represents the parse tree for expression (7↓3↑4↑3↓2)? |

| i ➥ |

| ii ➥ |

| iii ➥ |

| iv ➥ |

Show Answer With Best Explanation

Answer: II

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Precedence and Associativity | Help-Line |

| Q28➡ | Computer Organization On a non-pipelined sequential processor, a program segment, which is a part of the interrupt service routine, is given to transfer 500 bytes from an I/O device to memory. Initialize the address registerLOOP: Load a byte from deviceAssume that each statement in this program is equivalent to machine instruction which takes one clock cycle to execute if it is a non-load/store instruction. The load-store instructions take two clock cycles to execute. The designer of the system also has an alternate approach of using DMA controller to implement the same transfer. The DMA controller requires 20 clock cycles for initialization and other overheads. Each DMA transfer cycle takes two clock cycles to transfer one byte of data from the device to the memory. What is the approximate speedup when the DMA controller based design is used in place of the interrupt driven program based input-output? |

| i ➥ 3.4 |

| ii ➥ 4.4 |

| iii ➥ 5.1 |

| iv ➥ 6.7 |

Show Answer With Best Explanation

Answer: I

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | DMA | Help-Line |

| Q29➡ | Data Structures We are given a set of n distinct elements and an unlabeled binary tree with n nodes. In how many ways can we populate the tree with the given set so that it becomes a binary search tree? |

| i ➥ 0 |

| ii ➥ 1 |

| iii ➥ n! |

| iv ➥ |

Show Answer With Best Explanation

Answer: I

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Binary Trees | Help-Line |

| Q30➡ | Engineering Mathematics Which one of the following options is CORRECT given three positive integers x,y and z, and a predicate P(x) = ¬(x=1)∧∀y(∃z(x=y*z) ⇒ (y=x)∨(y=1)) |

| i ➥ P(x) being true means that x is a prime number |

| ii ➥ P(x) being true means that x is a number other than 1 |

| iii ➥ P(x) is always true irrespective of the value of x |

| iv ➥ P(x) being true means that x has exactly two factors other than 1 and x |

Show Answer With Best Explanation

Answer: I

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Propositional Logic | Help-Line |

| Q31➡ | Engineering Mathematics Given i=√-1, what will be the evaluation of the definite integral |

| i ➥ 0 |

| ii ➥ 2 |

| iii ➥ -i |

| iv ➥ i |

Show Answer With Best Explanation

Answer: IV

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Calculus | Help-Line |

| Q32➡ | Database Management System Consider a database table T containing two columns X and Y each of type integer. After the creation of the table, one record (X=1, Y=1) is inserted in the table. Let MX and My denote the respective maximum values of X and Y among all records in the table at any point in time. Using MX and MY, new records are inserted in the table 128 times with X and Y values being MX+1, 2*MY+1 respectively. It may be noted that each time after the insertion, values of MX and MY change. What will be the output of the following SQL query after the steps mentioned above are carried out? SELECT Y FROM T WHERE X=7; |

| i ➥ 127 |

| ii ➥ 255 |

| iii ➥ 129 |

| iv ➥ 257 |

Show Answer With Best Explanation

Answer: I

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | SQL | Help-Line |

| Q33➡ | Engineering Mathematics Consider a finite sequence of random values X = [x1, x2, …, xn]. Let μx be the mean and σx be the standard deviation of X. Let another finite sequence Y of equal length be derived from this as yi = a * xi + b, where a and b are positive constants. Let μy be the mean and σy be the standard deviation of this sequence. Which one of the following statements is INCORRECT? |

| i ➥ Index position of mode of X in X is the same as the index position of mode of Y in Y. |

| ii ➥ Index position of median of X in X is the same as the index position of median of Y in Y. |

| iii ➥ μy = aμx + b |

| iv ➥ σy = aσx + b |

Show Answer With Best Explanation

Answer: IV

Explanation: Upload Soon

| More Discussion | Explanation On YouTube | Probability | Help-Line |

| Q34➡ | |