| Q.1➡ | UGC NET DEC 2023 Which of the following circuit is used to store one bit of data ? |

| i ➥ Encoder |

| ii ➥ Decoder |

| iii ➥ Flip-Flop |

| iv ➥ Register |

| Best Explanation: Answer: (III) Explanation: Upload Soon |

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q2➡ | UGC NET DEC 2023 Identify the code sequence : 1010 1011 1001 1000 |

| i ➥ BCD |

| ii ➥ Excess-3 |

| iii ➥ Gray |

| iv ➥ Excess-3 gray |

| Best Explanation: Answer: (III) Explanation: Upload Soon |

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.3➡ | UGC NET JUNE 2023 Find the sum of all four digit numbers formed using the digits 1,2,4 and 6. |

| i ➥ 86,658 |

| ii ➥ 88,8858 |

| iii ➥ 91,958 |

| iv ➥ 93,358 |

| Best Explanation: Answer: I Explanation: Upload Soon |

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

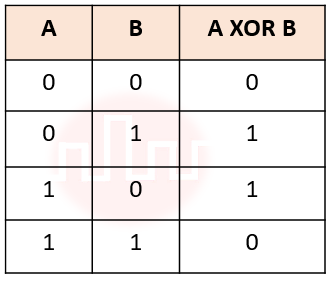

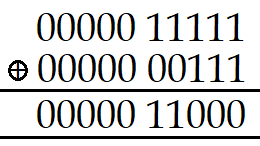

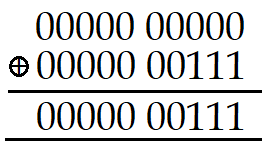

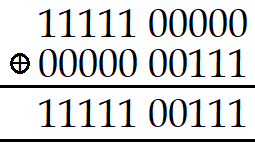

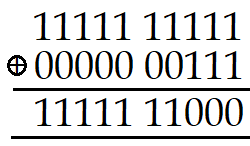

| Q.4➡ | UGC NET JUNE 2023 Let denote XOR operation. Let 1 and 0 denote the binary constants and F is the Boolean expression over two variables P and Q F(P,Q) = ((1⊕ P) ⊕(P⊕Q)) ⊕ ((P ⊕ Q) ⊕ (Q⊕0)) Which of the following is equivalent expression to F? |

| i ➥ P⊕Q |

| ii ➥ P+Q |

| iii ➥ (P+Q)’ |

| iv ➥ (P⊕Q)’ |

| Best Explanation: Answer: IV Explanation: (Repeated Question Please Remember this on |

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.5➡ | UGC NET JUNE 2023 What is the (4+4) fit binary fixed point equivalent of -(3.72)10 ? |

| i ➥ 0011.1100 |

| ii ➥ 0011.1010 |

| iii ➥ 1100.0100 |

| iv ➥ 0011.1011 |

| Best Explanation: Answer: III Explanation: Integer part: • The integer part of -3 is 33 in binary, which is 00110011 in 4 bits. Fractional part: • Convert the fractional part 0.720.72 to binary: • 0.72×2=1.440.72×2=1.44 (First bit: 1) • 0.44×2=0.880.44×2=0.88 (Next bit: 0) • 0.88×2=1.760.88×2=1.76 (Next bit: 1) Continuing this process: • 0.76×2=1.520.76×2=1.52 (Next bit: 1) • 0.52×2=1.040.52×2=1.04 (Next bit: 1) • 0.04×2=0.080.04×2=0.08 (Next bit: 0) • 0.08×2=0.160.08×2=0.16 (Next bit: 0) • The binary representation of 0.720.72 is 1011010010110100. Combine the binary representations: • Combine the integer and fractional parts with the binary point: • 0011.101101000011.10110100 Adjust to (4+4) fit binary fixed-point: • The total number of bits is 8 (4 bits for the integer part and 4 bits for the fractional part). • So, we need to truncate or round to fit into the (4+4) format. In this case, we truncate the extra bits. • The result is 1100.01001100.0100. Therefore, the correct answer is: iii ➥ 1100.0100 |

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.6➡ | NET December 2022 The memory size for n address lines and m data lines is given by |

| i ➥ 2m×n |

| ii ➥ m×n2 |

| iii ➥ 2n×m |

| iv ➥ n×m2 |

| Best Explanation: Answer: (iii) Explanation: Upload Soon |

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.7➡ | NET December 2022 Simplify the following using K-map F(A, B, C, D) = Σ(0, 2, 5, 7, 8, 10, 13, 15) |

| i ➥ BD + B’D’ |

| ii ➥ AC + A’C’ |

| iii ➥ BC + B’C’ |

| iv ➥ AD + A’D’ |

| Best Explanation: Answer: (i) Explanation: Upload Soon |

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.8➡ | NET June 2022 Consider a logic gate circuit, with 8 input lines (D0, D1………..D7) and 3 input Lines (A0, A1, A2) specified by following operations A2=D4+D5+D6+D7 A1=D2+D3+D6+D7 A0=D1+D3+D5+D0 Where + indicates logical OR operation. This circuit is |

| i ➥ 3×8 multiplexer |

| ii ➥ Decimal to BCD Converter |

| iii ➥ Octal to Binary encoder |

| iv ➥ Priority encoder |

| Best Explanation: Answer: (iv) Explanation: Upload Soon |

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.9➡ | NET June 2022 The number of gate inputs, required to realize expression ABC+AB̅CD+E Fbar+AD is |

| i ➥ 12 |

| ii ➥ 13 |

| iii ➥ 14 |

| iv ➥ 15 |

| Best Explanation: Answer: (iv) Explanation: Upload Soon |

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Question 10➡ | NTA UGC NET June 2021 The Octal equivalent of hexadecimal (D.C)16 is: |

| i ➥ (15.3)8 |

| ii ➥ (15.6)8 |

| iii ➥ (61.3)8 |

| iv ➥ (61.6)8 |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Number System | Help-Line |

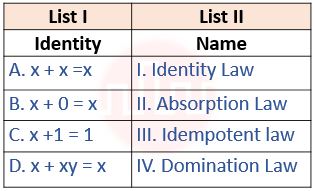

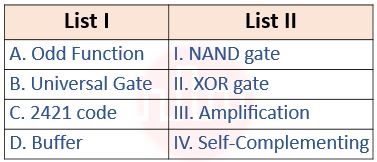

| Question .11➡ | NTA UGC NET June 2021 Match List I with List II  Choose the correct answer from the options given below: |

| i ➥ A – I, B -III , C – IV, D – II |

| ii ➥ A – III, B -I , C – II, D – IV |

| iii ➥ A – III, B -I , C – IV, D – II |

| iv ➥ A – III, B -IV , C – I, D – II |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Boolean Algebra | Help-Line |

| Question. 12➡ | NTA UGC NET June 2021 Match List I with List II  Choose the correct answer from the options given below: |

| i ➥ A – I, B – II, C – III, D – IV |

| ii ➥ A – I, B – III, C – II, D – IV |

| iii ➥ A – II, B – I, C – IV, D – III |

| iv ➥ A – IV, B – II, C – III, D – I |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Mixed | Help-Line |

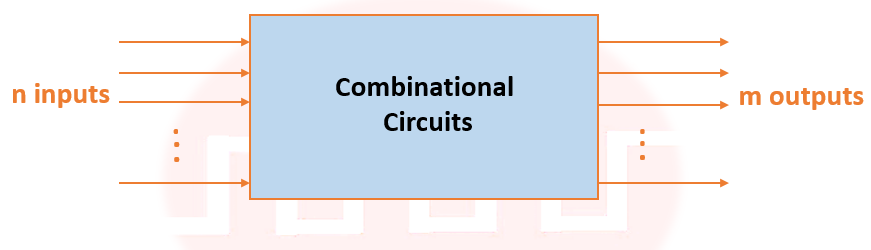

| Question .13➡ | NTA UGC NET June 2021 The characteristics of the combinational circuits are: A. Output at any time is function of inputs at that time B. Contains memory elements C. Do not have feedback paths D. Clock is used to trigger the circuits to obtain outputs Choose the correct answer from the options given below: |

| i ➥ A and B only |

| ii ➥ A and C only |

| iii ➥ B and C only |

| iv ➥ B and D only |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Combinational Circuits | Help-Line |

| Question .14➡ | NTA UGC NET June 2021 A digital computer has a common bus system for 8 registers 16 bits each. How many multiplexers are required to implement common bus? What size of multiplexers is required? |

| i ➥ 16, 16×1 |

| ii ➥ 16, 8×1 |

| iii ➥ 8, 16×1 |

| iv ➥ 8, 8×1 |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Combinational Circuits | Help-Line |

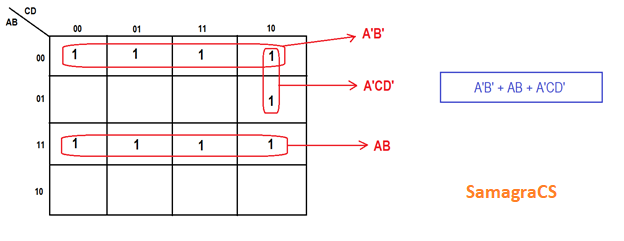

| Question .15➡ | NTA UGC NET November 2020 Simplified expression/s for following Boolean function F(A,B,C,D)=Σ(0,1,2,3,6,12,13,14,15) is/are A) A’B’+AB+A’C’D’ B) A’B’+AB+A’CD’ C) A’B’+AB+BC’D’ D) A’B’+AB+BCD’ Choose the correct answer from the options given below: |

| i ➥ (A) only |

| ii ➥ (B) only |

| iii ➥ (A) and (B) only |

| iv ➥ (B) and (D) only |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Boolean Algebra | Help-Line |

| Question .16➡ | NTA UGC NET November 2020 What kind of clauses are available in conjunctive normal form? |

| i ➥ Disjunction of literals |

| ii ➥ Disjunction of variables |

| iii ➥ Conjunction of literals |

| iv ➥ Conjunction of variables |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Boolean Algebra | Help-Line |

| Question .17➡ | NTA UGC NET November 2020 Consider a code with only four valid code words: 0000000000, 0000011111, 1111100000, and 1111111111. This code has distance 5. If the code word arrived is 0000000111 then the original code word must be _______. |

| i ➥ 0000011111 |

| ii ➥ 0000000000 |

| iii ➥ 1111100000 |

| iv ➥ 1111111111 |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Number System | Help-Line |

| Question .18➡ | NTA UGC NET December 2019 Which of the following binary codes for decimal digits are self complementing? (a) 8421 code (b) 2421 code (c) excess-3 code (d) excess-3 gray code Choose the correct option: |

| i ➥ (a) and (b) |

| ii ➥ (b) and (c) |

| iii ➥ (c) and (d) |

| iv ➥ (d) and (a) |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Number System | Help-Line |

| Question .19➡ | NTA UGC NET December 2019 The Boolean AB+AB’+A’C+AC is unaffected by the value of the Boolean variable ___________. |

| i ➥ A |

| ii ➥ B |

| iii ➥ C |

| iv ➥ A, B & C |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Boolean Algebra | Help-Line |

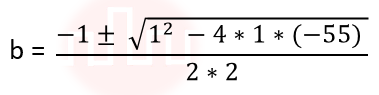

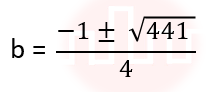

| Question .20➡ | NTA UGC NET December 2019 Given following equation: (142)b + (112)b-2 = (75)8 Find base b. |

| i ➥ 3 |

| ii ➥ 6 |

| iii ➥ 7 |

| iv ➥ 5 |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Number System | Help-Line |

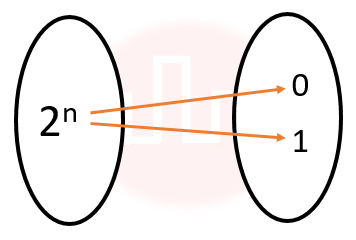

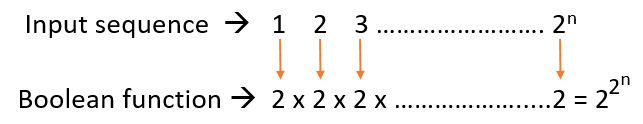

| Question .21➡ | NTA UGC NET June 2019 How many different Boolean functions of degree n are there? |

| i ➥ |

| ii ➥ (22)2 |

| iii ➥ 22n-1 |

| iv ➥ |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Boolean Algebra | Help-Line |

| Question .22➡ | NTA UGC NET June 2019 Consider the equation (146)b + (313)b-2 = (246)8 . Which of the following is the value of b? |

| i ➥ 8 |

| ii ➥ 7 |

| iii ➥ 10 |

| iv ➥ 16 |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Number System | Help-Line |

| Question .23➡ | NTA UGC NET June 2019 How many address lines and data lines are required to provide a memory capacity of 16K x 16? |

| i ➥ 10,4 |

| ii ➥ 16,16 |

| iii ➥ 14,16 |

| iv ➥ 4,16 |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Combinational Circuits | Help-Line |

| Question .24➡ | NTA UGC NET June 2019 Suppose that the register A and register K have the bit configuration. Only the three leftmost bits of A are compared with memory words because K has 1’s in these positions. Because of its organization, this type of memory is uniquely suited to parallel searches by data association. This type of memory is known as |

| i ➥ RAM |

| ii ➥ ROM |

| iii ➥ Content addressable memory |

| iv ➥ Secondary memory |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Combinational Circuits | Help-Line |

| Question .25➡ | NTA UGC NET June 2019 What will be the number of states when a MOD-2 counter is followed by a MOD-5 counter? |

| i ➥ 5 |

| ii ➥ 10 |

| iii ➥ 15 |

| iv ➥ 20 |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Sequential Circuits | Help-Line |

| Question .26➡ | NTA UGC NET June 2019 How many bit strings of length ten either start with a 1 bit or end with two bits 00? |

| i ➥ 320 |

| ii ➥ 480 |

| iii ➥ 640 |

| iv ➥ 768 |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Number System | Help-Line |

| Question .27➡ | NTA UGC NET June 2019 The parallel bus arbitration technique uses an external priority encoder and a decoder. Suppose, a parallel arbiter has 5 bus arbiters. What will be the size of priority encoder and decoder respectively? |

| i ➥ 4×2, 2×4 |

| ii ➥ 2×4, 4×2 |

| iii ➥ 3×8, 8×3 |

| iv ➥ 8×3, 3×8 |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Combinational Circuits | Help-Line |

| Question .28➡ | NTA UGC NET December 2018 In computers, subtraction is generally carried out by |

| i ➥ 1’s complement |

| ii ➥ 10’s complement |

| iii ➥ 2’s complement |

| iv ➥ 9’s complement |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Number System | Help-Line |

| Question .29➡ | NTA UGC NET December 2018 The boolean expression A’⋅B+A.B’+A.B is equivalent to |

| i ➥ A+B |

| ii ➥ A.B |

| iii ➥ (A+B)’ |

| iv ➥ A’.B |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Boolean Algebra | Help-Line |

| Question .30➡ | NTA UGC NET December 2018 The relation ≤ and < on a boolean algebra are defined as : x ≤ y and only if x ∨ y = y x < y means x ≤ y but x ≠ y x ≥ y means y ≤ x and x > y means y <x Consider the above definitions, which of the following is not true in the boolean algebra ? (i)If x ≤ y and y ≤ z, then x ≤ z (ii)If x ≤ y and y ≤ x, then x=y (iii)If x < y and y < z, then x ≤ y (iv)If x < y and y < z, then x < y |

| i ➥ (iv) only |

| ii ➥ (iii) only |

| iii ➥ (i) and (ii) only |

| iv ➥ (ii) and (iii) only |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Boolean Algebra | Help-Line |

| Question .31➡ | NTA UGC NET December 2018 Consider the following boolean equations : (i) wx + w(x + y) + x(x + y)=x+wy (ii) (wx’(y+xz’)+w’x’)y=x’y What can you say about the above equations ? |

| i ➥ Both (i) and (ii) are true |

| ii ➥ (i) is true and (ii) is false |

| iii ➥ Both (i) and (ii) are false |

| iv ➥ (i) is false and (ii) is true |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Boolean Algebra | Help-Line |

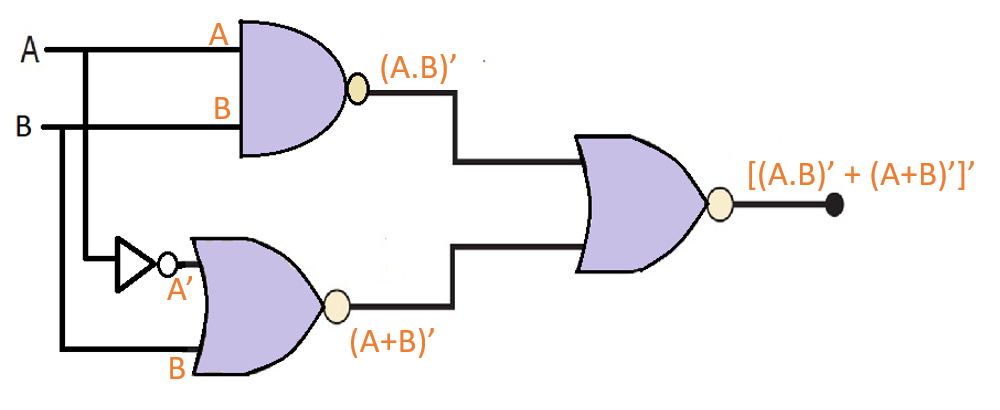

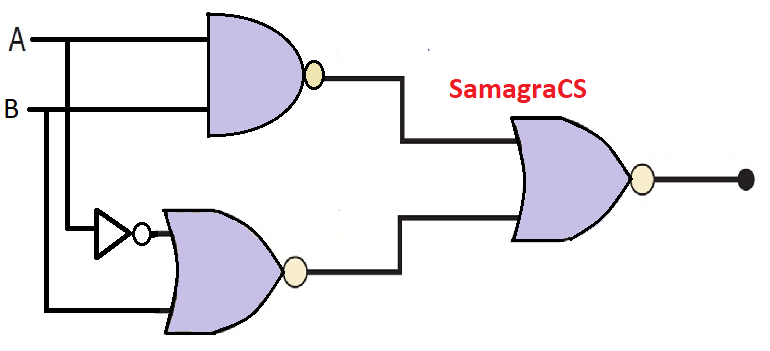

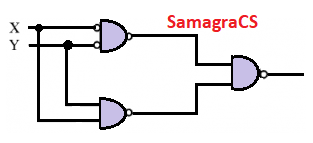

| Question .32➡ | NTA UGC NET December 2018 Find the boolean expression for the logic circuit shown below : (1-NAND gate, 2-NOR gate, 3-NOR gate)  |

| i ➥ AB |

| ii ➥ AB’ |

| iii ➥ A’B’ |

| iv ➥ A’B |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Boolean Algebra | Help-Line |

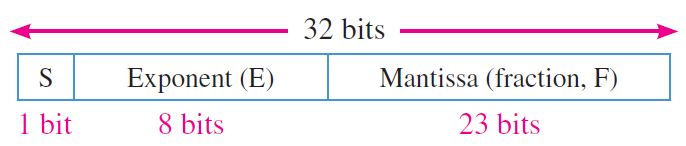

| Question .34➡ | NTA UGC NET December 2018 The decimal floating point number -40.1 represented using IEEE-754 32-bit representation and written in hexadecimal form is |

| i ➥ 0xC2206000 |

| ii ➥ 0xC2006666 |

| iii ➥ 0xC2006000 |

| iv ➥ 0xC2206666 |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Number System | Help-Line |

| Question .35➡ | NTA UGC NET December 2018 Which of the following statements are true ? (i) Every logic network is equivalent to one using just NAND gates or just NOR gates. (ii) Boolean expressions and logic networks correspond to labelled acyclic digraphs. (iii) No two Boolean algebras with n atoms are isomorphic. (iv) Non-zero elements of finite Boolean algebras are not uniquely expressible as joins of atoms. |

| i ➥ (i) and (iv) only |

| ii ➥ (i) and (ii) only |

| iii ➥ (i), (ii) and (iii) only |

| iv ➥ (ii), (iii) and (iv) only |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Boolean Algebra | Help-Line |

| Question .36➡ | NTA UGC NET June 2018 To guarantee correction of upto t errors, the minimum Hamming distance dmin in a block code must be__________. |

| i ➥ t+1 |

| ii ➥ t−2 |

| iii ➥ 2t−1 |

| iv ➥ 2t+1 |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Number System | Help-Line |

| Question .37➡ | NTA UGC NET June 2018 CMOS is a Computer Chip on the motherboard, which is : |

| i ➥ RAM |

| ii ➥ ROM |

| iii ➥ EPROM |

| iv ➥ Auxiliary storage |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Combinational Circuits | Help-Line |

| Question .38➡ | NTA UGC NET June 2018 In RS flip-flop, the output of the flip-flop at time (t+1) is same as the output at time t, after the occurrence of a clock pulse if : |

| i ➥ S=R=1 |

| ii ➥ S=0, R=1 |

| iii ➥ S=1, R=0 |

| iv ➥ S=R=0 |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Sequential Circuits | Help-Line |

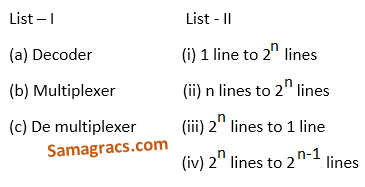

| Question .39➡ | NTA UGC NET June 2018 Match the terms in List – I with the options given in List – II :  |

| i ➥ (a)-(ii), (b)-(i), (c)-(iii) |

| ii ➥ (a)-(ii), (b)-(iii), (c)-(i) |

| iii ➥ (a)-(ii), (b)-(i), (c)-(iv) |

| iv ➥ (a)-(iv), (b)-(ii), (c)-(i) |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Combinational Circuits | Help-Line |

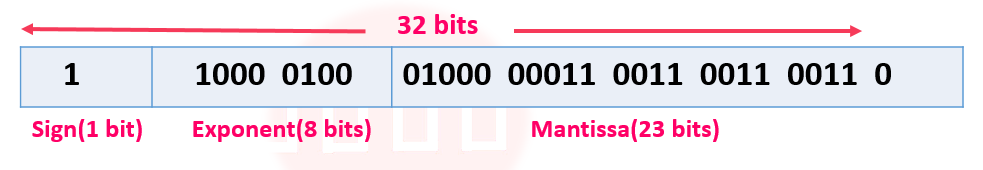

| Question .40➡ | NTA UGC NET June 2018 What does the following logic diagram represent ?  |

| i ➥ Synchronous Counter |

| ii ➥ Ripple Counter |

| iii ➥ Combinational Circuit |

| iv ➥ Mod 2 Counter |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Sequential Circuits | Help-Line |

| Question .41➡ | NTA UGC NET June 2018 Perform the following operation for the binary equivalent of the decimal numbers (-14)10+(15)10 The solution in 8 bit representation is : |

| i ➥ 11100011 |

| ii ➥ 00011101 |

| iii ➥ 10011101 |

| iv ➥ 11110011 |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Number System | Help-Line |

| Question .42➡ | NTA UGC NET June 2018 Simplify the following using K-map : F (A, B, C, D) = Σ (0, 1, 2, 8, 9, 12, 13) + d(A, B, C, D) = Σ (10, 11, 14, 15) d stands for don’t care condition. |

| i ➥ A+B’D’ + BC |

| ii ➥ A+B’D’ + B’C’ |

| iii ➥ A’+B’C’ |

| iv ➥ A’+B’C’+B’D’ |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Boolean Algebra | Help-Line |

| Question .43➡ | NTA UGC NET November 2017 Paper III Let P, Q, R and S be Propositions. Assume that the equivalences P ⇔ (Q ∨ ¬ Q) and Q ⇔ R hold.Then the truth value of the formula (P ∧ Q) ⇒ ((P ∧ R) ∨ S) is always: |

| i ➥ True |

| ii ➥ False |

| iii ➥ Same as truth table of Q |

| iv ➥ Same as truth table of S |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Boolean Algebra | Help-Line |

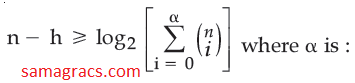

| Question .43➡ | NTA UGC NET November 2017 Paper III For any binary (n, h) linear code with minimum distance (2t+1) or greater  |

| i ➥ 2t+1 |

| ii ➥ t+1 |

| iii ➥ t |

| iv ➥ t-1 |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Number System | Help-Line |

| Question .44➡ | NTA UGC NET November 2017 Paper II If the time is now 4 O’clock, what will be the time after 101 hours from now ? |

| i ➥ 9 O’Clock |

| ii ➥ 8 O’Clock |

| iii ➥ 5 O’Clock |

| iv ➥ 4 O’Clock |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Sequential Circuits | Help-Line |

| Question 45➡ | NTA UGC NET November 2017 Paper II Let m=(313)4 and n=(322)4 . Find the base 4 expansion of m+n. |

| i ➥ (635)4 |

| ii ➥ (32312)4 |

| iii ➥ (21323)4 |

| iv ➥ (1301)4 |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Number System | Help-Line |

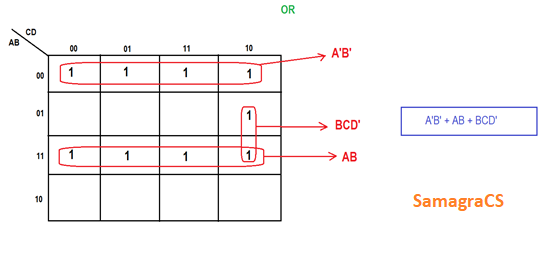

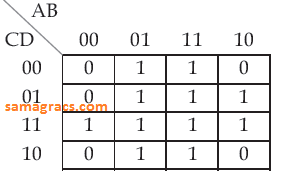

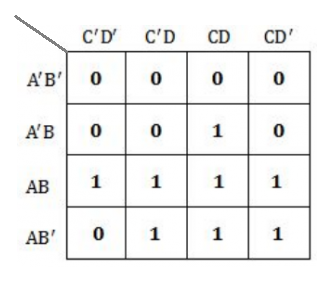

| Question .46➡ | NTA UGC NET November 2017 Paper II The Boolean function with the Karnaugh map  |

| i ➥ (A+C).D+B |

| ii ➥ (A+B).C+D |

| iii ➥ (A+D).C+B |

| iv ➥ (A+C).B+D |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Boolean Algebra | Help-Line |

| Question .47➡ | NTA UGC NET November 2017 Paper II The Octal equivalent of the binary number 1011101011 is : |

| i ➥ 7353 |

| ii ➥ 1353 |

| iii ➥ 5651 |

| iv ➥ 5657 |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Number System | Help-Line |

| Question .48➡ | NTA UGC NET November 2017 Paper II Let P and Q be two propositions, ¬ (P ↔ Q) is equivalent to: |

| i ➥ P ↔ ¬ Q |

| ii ➥ ¬ P ↔ Q |

| iii ➥ ¬ P ↔ ¬ Q |

| iv ➥ Q → P |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Boolean Algebra | Help-Line |

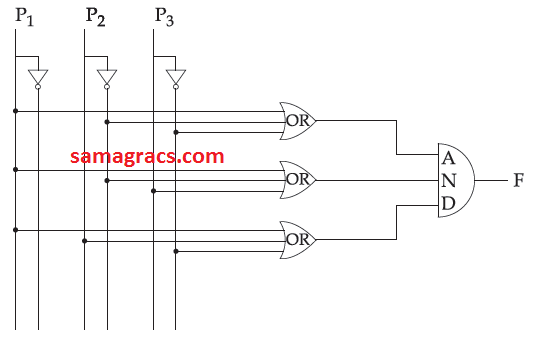

| Question .49➡ | NTA UGC NET November 2017 Paper II The output of the following combinational circuit is F:  The value of F is : |

| i ➥ P1+P’2P3 |

| ii ➥ P1+P’2P’3 |

| iii ➥ P1 +P2 P’3 |

| iv ➥ P’1 +P2 P3 |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Boolean Algebra | Help-Line |

| Question .50➡ | NTA UGC NET January 2017 Paper III Let C be a binary linear code with minimum distance 2t + 1 then it can correct upto______bits of error. |

| i ➥ t + 1 |

| ii ➥ t |

| iii ➥ t – 2 |

| iv ➥ t / 2 |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Number System | Help-Line |

| Question .51➡ | NTA UGC NET January 2017 Paper II ECL is the fastest of all logic families. High speed in ECL is possible because transistors are used in difference amplifier configuration, in which they are never driven into __. |

| i ➥ Race condition |

| ii ➥ Saturation |

| iii ➥ Delay |

| iv ➥ High impedance |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Sequential Circuits | Help-Line |

| Question .52➡ | NTA UGC NET January 2017 Paper II A binary 3 bit down counter uses J-K flip-flops, FFi with inputs Ji , Ki and outputs Qi , i=0,1,2 respectively. The minimized expression for the input from following, is I. J0 = K0 = 0 II. J0 = K0 = 1 III. J1 = K1 = Q0 IV. J1 = K1 =Q’0 V. J2 = K2 = Q1 Q0 VI. J2 = K2 = Q’1 Q’0 |

| i ➥ I,III,V |

| ii ➥ I,IV,VI |

| iii ➥ II,III,V |

| iv ➥ II,IV,VI |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Sequential Circuits | Help-Line |

| Question .53➡ | NTA UGC NET January 2017 Paper II Convert the octal number 0.4051 into its equivalent decimal number: |

| i ➥ 0.5100098 |

| ii ➥ 0.2096 |

| iii ➥ 0.52 |

| iv ➥ 0.4192 |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Number System | Help-Line |

| Question .54➡ | NTA UGC NET January 2017 Paper II The hexadecimal equivalent of the octal number 2357 is : |

| i ➥ 2EE |

| ii ➥ 2FF |

| iii ➥ 4EF |

| iv ➥ 4FE |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Number System | Help-Line |

| Question .55➡ | NTA UGC NET January 2017 Paper II If X is a binary number which is power of 2, then the value of X & (X – 1) is : |

| i ➥ 11….11 |

| ii ➥ 00…..00 |

| iii ➥ 100…..0 |

| iv ➥ 000……1 |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Number System | Help-Line |

| Question .56➡ | NTA UGC NET August 2016 Paper II Which of the following logic expressions is incorrect? |

| i ➥ 1 ⊕ 0 = 1 |

| ii ➥ 1 ⊕ 1 ⊕ 1 = 1 |

| iii ➥ 1 ⊕ 1 ⊕ 0 = 1 |

| iv ➥ 1 ⊕ 1 = 0 |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Boolean Algebra | Help-Line |

| Question .57➡ | NTA UGC NET August 2016 Paper II The IEEE-754 double-precision format to represent floating point numbers, has a length of _ bits. |

| i ➥ 16 |

| ii ➥ 32 |

| iii ➥ 48 |

| iv ➥ 64 |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Number System | Help-Line |

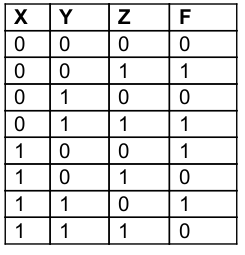

| Question .58➡ | NTA UGC NET August 2016 Paper II Simplified Boolean equation for the following truth table is:  |

| i ➥ F = yz’ + y’z |

| ii ➥ F = xy’ + x’y |

| iii ➥ F = x’z + xz’ |

| iv ➥ F = x’z + xz’ + xyz |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Boolean Algebra | Help-Line |

| Question .59➡ | NTA UGC NET August 2016 Paper II The simplified form of a Boolean equation (AB’ + AB’C + AC) (A’C’ + B’) is : |

| i ➥ AB’ |

| ii ➥ AB’C |

| iii ➥ A’B |

| iv ➥ ABC |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Boolean Algebra | Help-Line |

| Question .60➡ | NTA UGC NET August 2016 Paper II In a positive-edge-triggered JK flip-flop, if J and K both are high then the output will be _________ on the rising edge of the clock. |

| i ➥ No change |

| ii ➥ Set |

| iii ➥ Reset |

| iv ➥ Toggle |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Sequential Circuits | Help-Line |

| Question .61➡ | NTA UGC NET August 2016 Paper III A ripple counter is a : |

| i ➥ Synchronous Counter |

| ii ➥ Asynchronous counter |

| iii ➥ Parallel counter |

| iv ➥ None of the above |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Sequential Circuits | Help-Line |

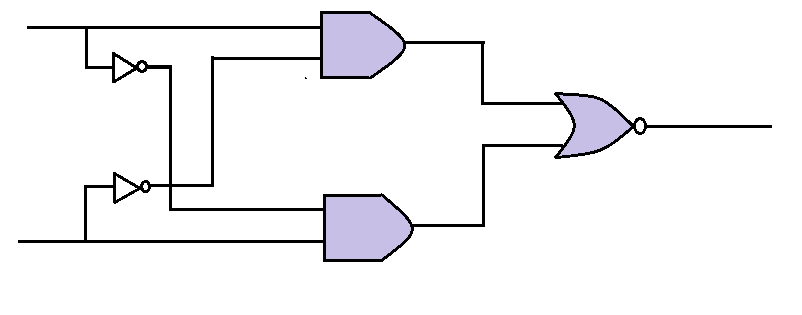

| Question .62➡ | NTA UGC NET August 2016 Paper II The output of the following combinational circuit.  |

| i ➥ X.Y |

| ii ➥ X+Y |

| iii ➥ X⊕Y |

| iv ➥ (X⊕Y)’ |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Boolean Algebra | Help-Line |

| Question .63➡ | NTA UGC NET July 2016 Paper II The octal number 326.4 is equivalent to |

| i ➥ (214.2)10 and (D6.8))16 |

| ii ➥ (212.5)10 and (D6.8))16 |

| iii ➥ (214.5)10 and (D6.8))16 |

| iv ➥ (214.5)10 and (D6.4))16 |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Number System | Help-Line |

| Question .64➡ | NTA UGC NET July 2016 Paper II Which of the following is the most efficient to perform arithmetic operations on the numbers? |

| i ➥ Sign-magnitude |

| ii ➥ 1’s complement |

| iii ➥ 2’s complement |

| iv ➥ 9’s complement |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Number System | Help-Line |

| Question .65➡ | NTA UGC NET July 2016 Paper II The Karnaugh map for a Boolean function is given as  The simplified Boolean equation for the above Karnaugh Map is |

| i ➥ AB + CD + AB’ + AD |

| ii ➥ AB + AC + AD + BCD |

| iii ➥ AB + AD + BC + ACD |

| iv ➥ AB + AC + BC + BCD |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Boolean Algebra | Help-Line |

| Question .66➡ | NTA UGC NET July 2016 Paper II Which of the following logic operations is performed by the following given combinational circuit?  |

| i ➥ EXCLUSIVE-OR |

| ii ➥ EXCLUSIVE-NOR |

| iii ➥ NAND |

| iv ➥ NOR |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Boolean Algebra | Help-Line |

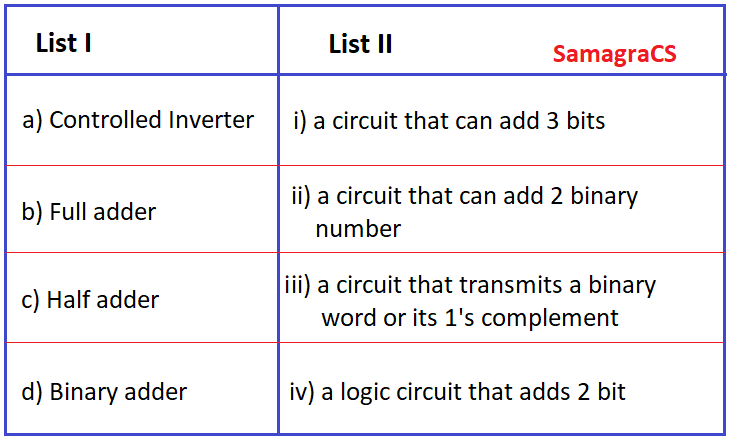

| Question .67➡ | NTA UGC NET July 2016 Paper II Match the following:  |

| i ➥ a-iii, b-ii, c-iv, d-i |

| ii ➥ a-ii, b-iv, c-i, d-iii |

| iii ➥ a-ii, b-i, c-iv, d-iii |

| iv ➥ a-iii, b-i, c-iv, d-ii |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Combinational Circuits | Help-Line |

| Question .68➡ | NTA UGC NET July 2016 Paper III Which of the following is a sequential circuit? |

| i ➥ Multiplexer |

| ii ➥ Decoder |

| iii ➥ Counter |

| iv ➥ Full adder |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Sequential Circuits | Help-Line |

| Question .69➡ | NTA UGC NET December 2015 Paper III The three outputs X1X2X3 from the 8 X 3 priority encoder are used to provide a vector address of the form 101X1X2X300. What is the second highest priority vector address in hexadecimal if the vector addresses are starting from the one with the highest priority ? |

| i ➥ BC |

| ii ➥ A4 |

| iii ➥ BD |

| iv ➥ AC |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Combinational Circuits | Help-Line |

| Question .70➡ | NTA UGC NET December 2014 Paper II The BCD adder to add two decimal digits needs minimum of |

| i ➥ 6 full adders and 2 half adders |

| ii ➥ 5 full adders and 3 half adders |

| iii ➥ 4 full adders and 3 half adders |

| iv ➥ 5 full adders and 2 half adders |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Combinational Circuits | Help-Line |

| Question .71➡ | NTA UGC NET December 2014 Paper II The Excess-3 decimal code is a self-complementing code because |

| i ➥ The binary sum of a code and its 9’s complement is equal to 9. |

| ii ➥ It is a weighted code |

| iii ➥ Complement can be generated by inverting each bit pattern |

| iv ➥ The binary sum of a code and its 10’s complement is equal to 9 |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Number System | Help-Line |

| Question .72➡ | NTA UGC NET December 2014 Paper II The range of representable normalized numbers in the floating point binary fractional representation in a 32-bit word with 1-bit sign, 8-bit excess 128 biased exponent and 23-bit mantissa is |

| i ➥ 2-128 to (1 – 2–23 ) * 2127 |

| ii ➥ (1 – 2–23 ) * 2-127 to 2128 |

| iii ➥ (1 – 2–23 ) * 2–127 to 223 |

| iv ➥ 2–129 to (1 – 2–23 ) * 2127 |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Number System | Help-Line |

| Question .73➡ | NTA UGC NET June 2014 Paper II A Boolean function F is called self-dual if and only if F(x1, x2, … xn) = F (͞x1,͞x2, …͞xn) How many Boolean functions of degree n are self-dual ? |

| i ➥ 2n |

| ii ➥ (2)2^n |

| iii ➥ (2)n^2 |

| iv ➥ (2)(2^(n-1)) |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Boolean Algebra | Help-Line |

| Question .74➡ | NTA UGC NET June 2014 Paper II Which of the following statement(s) is (are) not correct ? i. The 2’s complement of 0 is 0. ii. In 2’s complement, the left most bit cannot be used to express a quantity. iii. For an n-bit word (2’s complement) which includes the sign bit, there are 2n–1 positive integers, 2n+1 negative integers and one 0 for a total of 2n unique states. iv. In 2’s complement the significant information is contained in the 1’s of positive numbers and 0’s of the negative numbers. |

| i ➥ i & iv |

| ii ➥ i & ii |

| iii ➥ iii |

| iv ➥ iv |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Number System | Help-Line |

| Question .75➡ | NTA UGC NET June 2014 Paper III The output of a sequential circuit depends on |

| i ➥ Present input only |

| ii ➥ Both present and past input |

| iii ➥ Past output only |

| iv ➥ None of the above |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Sequential Circuits | Help-Line |

| Question .76➡ | NTA UGC NET June 2014 Paper III Which of the following flip-flops is free from race condition ? |

| i ➥ T flip-flop |

| ii ➥ SR flip-flop |

| iii ➥ Master-slave JK flip-flop |

| iv ➥ None of the above |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Sequential Circuits | Help-Line |

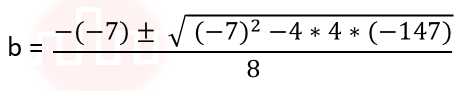

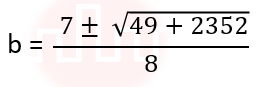

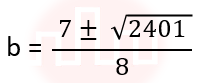

| Question .77➡ | NTA UGC NET June 2014 Paper III A terminal multiplexer has six 1200 bps terminals and ‘n’ 300 bps terminals connected to it. If the outgoing line is 9600 bps, what is the value of n ? |

| i ➥ 4 |

| ii ➥ 8 |

| iii ➥ 16 |

| iv ➥ 28 |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Combinational Circuits | Help-Line |

| Question .78➡ | NTA UGC NET December 2013 Paper III Which of the following statements are true ? a. A circuit that adds two bits, producing a sum bit and a carry bit is called half adder. b. A circuit that adds two bits, producing a sum bit and a carry bit is called full adder. c. A circuit that adds two bits and a carry bit producing a sum bit and a carry bit is called full adder. d. A device that accepts the value of a Boolean variable as input and produces its complement is called an inverter. |

| i ➥ a and b |

| ii ➥ b and c |

| iii ➥ a, b and c |

| iv ➥ a, c and d |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Combinational Circuits | Help-Line |

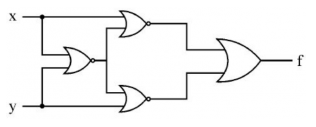

| Question .79➡ | NTA UGC NET December 2013 Paper III What will be the output of the following logic diagram?  |

| i ➥ x OR y |

| ii ➥ x AND y |

| iii ➥ x XOR y |

| iv ➥ x XNOR y |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Boolean Algebra | Help-Line |

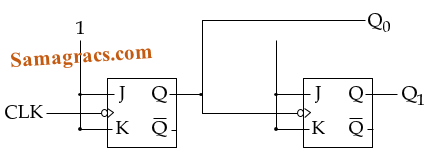

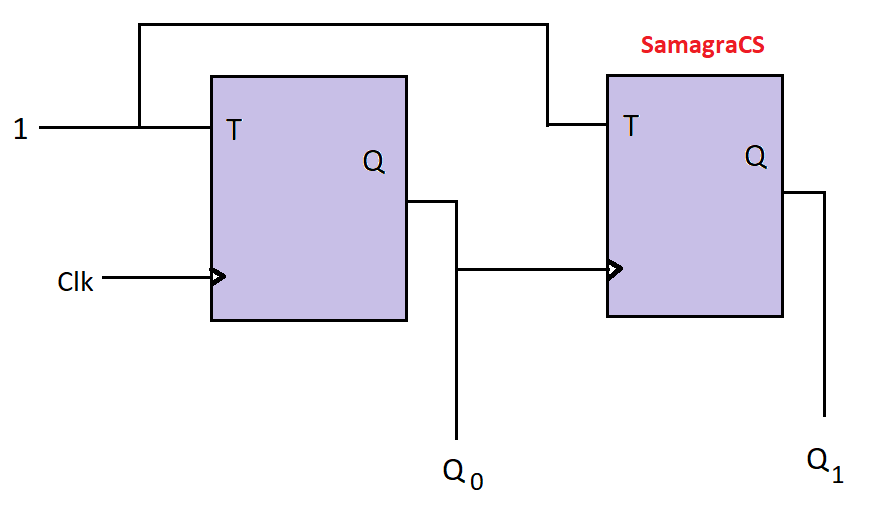

| Question .80➡ | NTA UGC NET December 2013 Paper III What are the final values of Q1 and Q0 after 4 clock cycles, if initial values are 00 in the sequential circuit shown below:  |

| i ➥ 11 |

| ii ➥ 10 |

| iii ➥ 01 |

| iv ➥ 00 |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Sequential Circuits | Help-Line |

| Question .81➡ | NTA UGC NET December 2013 Paper III Synchronization is achieved by a timing device called_________ a which generates a periodic train of ________. |

| i ➥ clock generator, clock pulse |

| ii ➥ master generator, clock pulse |

| iii ➥ generator, clock |

| iv ➥ master clock generator, clock pulse |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Sequential Circuits | Help-Line |