Machine Instruction COA

| Q1➡ | A processor has 40 distinct instructions and 24 general purpose registers. A 32-bit instruction word has an opcode, two register operands and an immediate operand. The number of bits available for the immediate operand field is __. |

| i ➥ 19 bits |

| ii ➥ 17 bits |

| iii ➥ 16 bits |

| iv ➥ 18 bits |

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q2➡ | For computers based on three-address instruction formats, each address field can be used to specify which of the following: (S1) A memory operand. (S2) A processor register. (S3) An implied accumulator register. |

| i ➥ Only S2 and S3 |

| ii ➥ Either S1 or S2 |

| iii ➥ Either S2 or S3 |

| iv ➥ All of S1, S2 and S3 |

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q3➡ | A machine has a 32-bit architecture, with 1-word long instructions. It has 64 registers, each of which is 32 bits long. It needs to support 45 instructions, which have an immediate operand in addition to two register operands. Assuming that the immediate operand is an unsigned integer, the maximum value of the immediate operand is __. |

| i ➥ 16386 |

| ii ➥ 16385 |

| iii ➥ 16384 |

| iv ➥ 16383 |

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q4➡ | Consider a hypothetical processor with an instruction of type LW R1, 20 (R2), which during execution reads a 32-bit word from memory and stores it in a 32-bit register R1. The effective address of the memory location is obtained by the addition of constant 20 and the contents of register R2. Which of the following best reflects the addressing mode implemented by this instruction for the operand memory? |

| i ➥ Base Indexed Addressing |

| ii ➥ Register Indirect Scaled Addressing |

| iii ➥ Register Addressing |

| iv ➥ Immediate Addressing |

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q5➡ | A CPU has 24-bit instructions. A program starts at address 300 (in decimal). Which one of the following is a legal program counter (all values in decimal)? |

| i ➥ 700 |

| ii ➥ 600 |

| iii ➥ 500 |

| iv ➥ 400 |

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q6➡ | The part of machine level instruction, which tells the central processor what has to be done, is |

| i ➥ Address |

| ii ➥ Locator |

| iii ➥ Flip flop |

| iv ➥ Operation code |

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q7➡ | Which of the following is not a form of main memory? |

| i ➥ Instruction cache |

| ii ➥ Instruction register |

| iii ➥ Translation lookaside buffer |

| iv ➥ Instruction Opcode |

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

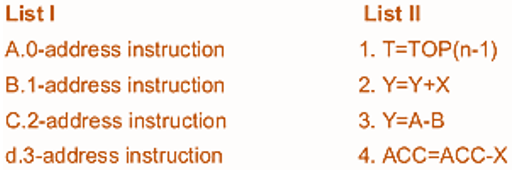

| Q8➡ | Match list I with list II and select the correct answer using the codes given below the lists.  |

| i ➥ 3 2 4 1 |

| ii ➥ 1 2 3 4 |

| iii ➥ 2 3 1 4 |

| iv ➥ 1 4 2 3 |

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q9➡ | Which of the following is not a program instruction? |

| i ➥ CALL |

| ii ➥ JMP |

| iii ➥ MOV |

| iv ➥ CMP |

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |