Computer System Architecture Subject Wise UGC NET Question Analysis

Computer System Architecture PYQ Part-2

| Q.1➡ | UGC NET DEC 2023 The average time required to search a storage location in memory and obtain its contents is called: |

| i ➥ Access time |

| ii ➥ Latency time |

| iii ➥ Response time |

| iv ➥ Reading time |

| Best Explanation: Answer: (I) Explanation: Upload Soon |

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.2➡ | UGC NET DEC 2023 Match List – I with List – II. List – I (A) SZA (B) SKI (C) SNA (D) ISZ List – II (I) Increment M and skip it zero (II) Skip if AC is negative (III) Skip if input flag is on (IV) Skip if AC is Zero Choose the correct answer from the options given below : |

| i ➥ (A)-(II), (B)-(IV), (C)-(I), (D)-(III) |

| ii ➥ (A)-(IV), (B)-(III), (C)-(II), (D)-(I) |

| iii ➥ (A)-(IV), (B)-(II), (C)-(I), (D)-(III) |

| iv ➥ (A)-(III), (B)-(IV), (C)-(II), (D)-(I) |

| Best Explanation: Answer: (II) Explanation: Upload Soon |

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.3➡ | UGC NET DEC 2023 The microoperation which divides a signed binary number by 2 is: |

| i ➥ Circular shift |

| ii ➥ Logical shift |

| iii ➥ Arithmetic shift right |

| iv ➥ Arithmetic shift left |

| Best Explanation: Answer: (II) Explanation: Upload Soon |

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.4➡ | UGC NET DEC 2023 Which of the following statements is/are NOT CORRECT about NUMA? (A) LOAD and STORE instructions are used to access remote memory. (B) There is a single address space visible to all CPU. (C) Access to local memory is slower than access to remote memory. (D) When the access time to remote memory is hidden, the system is called NC – NUMA. (E) In CC-NUMA, Coherent caches are present. Choose the correct answer from the options given below : |

| i ➥ (A) and (C) Only |

| ii ➥ (B) and (D) Only |

| iii ➥ (A) and (E) Only |

| iv ➥ (C) and (D) Only |

| Best Explanation: Answer: (IV) Explanation: Upload Soon |

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.5➡ | UGC NET DEC 2023 The interface(s) that provide(s) I/O transfer of data directly to and from the memory unit peripheral is/are termed as: (A) DMA (Direct Memory Access) (B) IOP (Input-Output Processor) (C) Serial Interface (D) Parallel Interface Choose the correct answer from the options given below : |

| i ➥ (A) Only |

| ii ➥ (B) Only |

| iii ➥ (A) and (B) Only |

| iv ➥ (C) and (D) Only |

| Best Explanation: Answer: (III) Explanation: Upload Soon |

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.6➡ | UGC NET DEC 2023 A system bus in which each data item is transferred during a time slice known in advance to both units source and destination is called: |

| i ➥ MIMD |

| ii ➥ DMA |

| iii ➥ asynchronous bus |

| iv ➥ synchronous bus |

| Best Explanation: Answer: (IV) Explanation: Upload Soon |

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.7➡ | UGC NET DEC 2023 In most general case, the computer needs to process each instruction with the following sequence of steps: (A) Calculate the effective address (B) Execute the instruction (C) Fetch the instruction from memory (D) Fetch the operand from memory (E) Decode the instruction Choose the correct answer from the options given below: |

| i ➥ (A), (B), (C), (D), (E) |

| ii ➥ (A), (B), (C), (E), (D) |

| iii ➥ (C), (E), (A), (D), (B) |

| iv ➥ (C), (E), (D), (A), (B) |

| Best Explanation: Answer: (III) Explanation: Upload Soon |

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.8➡ | UGC NET JUNE 2023 A processor chip is used for application in which 30% of execution time is spent on floating point addition. For the new model of the processor, the design team has come up with redesign the floating point adder to make it twice as fast. What will be possible maximum speed up by this redesign? |

| i ➥ 2.0 |

| ii ➥ 1.06 |

| iii ➥ 1.18 |

| iv ➥ 2.5 |

| Best Explanation: Answer: III Explanation: Upload Soon |

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.9➡ | UGC NET JUNE 2023 256Mb DRAM is organized as a 32M×8 memory externally and as a 16 K×16 K square array internally. Each row must be refreshed at least once every 50 mili second to forestall loss of data; refreshing one row takes 100 nanoseconds. What fraction of the total memory bandwidth is lost to refresh cycles? |

| i ➥ 6.6% |

| ii ➥ 3.3% |

| iii ➥ 9.9% |

| iv ➥ 4.3% |

| Best Explanation: Answer: II Explanation: Upload Soon |

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.10➡ | NET December 2022 Which one of the following type of memory is fastest |

| i ➥ Cache memory |

| ii ➥ Register memory |

| iii ➥ Main memory |

| iv ➥ Secondary memory |

| Best Explanation: Answer: (ii) Explanation: Upload Soon |

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.11➡ | NET December 2022 Consider an unpipelined machine with 10nsec clock cycles which uses four cycles for ALU operations and branches where as five cycles for memory operation. Assume that the relative frequencies of these operations are : 40%, 20% and 40 %, respectively. Due to clock skew and setup pipeline let us consider that the machine adds one nsec overhead to the clock. How much speedup is observed in the instruction execution rate when a pipelined machine is considered? |

| i ➥ 2 times |

| ii ➥ 4 times |

| iii ➥ 6 times |

| iv ➥ 8 times |

| Best Explanation: Answer: (ii) Explanation: Upload Soon |

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.12➡ | NET December 2022 Which of the following is/are true for Dynamic RAM (DRAM) ? (A) It is slower than static RAM (SRAM) (B) Packing Density is Higher than Static RAM (SRAM) (C) It’s faster than Static RAM (SRAM) (D) It is requires data refreshing which of the correct answer from the options given below : |

| i ➥ A, B and D only |

| ii ➥ A, B and C only |

| iii ➥ C and D only |

| iv ➥ B and D only |

| Best Explanation: Answer: (i) Explanation: Upload Soon |

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.13➡ | NET December 2022 Which of the following statement is/are false? A : The processor has direct access to both primary and secondary memory B : Primary memory stores the active instructions and data for the program being executed on the process C : Secondary memory is used as a backup memory D : memory system is implemented on a single level memory Choose the correct answer from the options given below : |

| i ➥ A and B only |

| ii ➥ B and C only |

| iii ➥ A, B and C only |

| iv ➥ A and D only |

| Best Explanation: Answer: (iv) Explanation: Upload Soon |

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

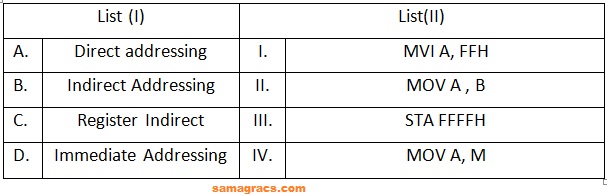

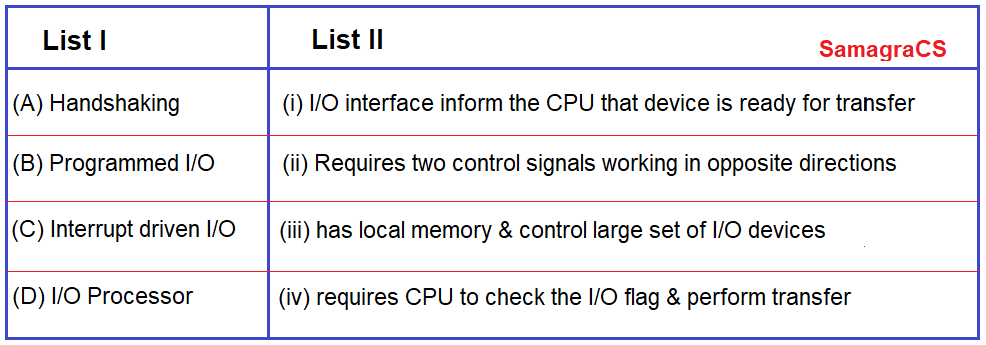

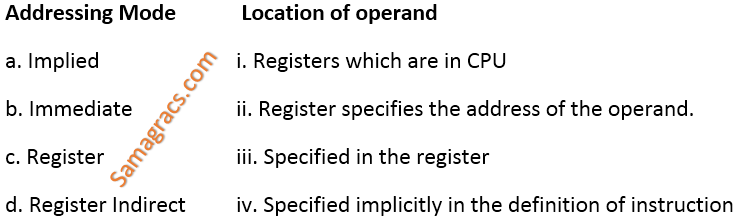

| Q.14➡ | NET December 2022 Match List (I) with List (II)  Choose the correct answer from the options given below: |

| i ➥ A-(I), B-(II), C-(III), D-(IV) |

| ii ➥ A-(II), B-(III), C-(IV), D-(I) |

| iii ➥ A-(III), B-(IV), C-(II), D-(I) |

| iv ➥ A-(IV), B-(III), C-(I), D-(II) |

| Best Explanation: Answer: (iii) Explanation: Upload Soon |

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.15➡ | NET December 2022 The Correct sequence in fetch- executes cycle is …………. (A) Decode (B) Fetch (C) Execute Choose the correct answer from the following |

| i ➥ A-B-C |

| ii ➥ B-C-A |

| iii ➥ C-B-A |

| iv ➥ B-A-C |

| Best Explanation: Answer: (iv) Explanation: Upload Soon |

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.16➡ | NET June 2022 In a cache memory , if address has 9 bits in Tag field and 12 bits in index field, the size of main memory and cache memory would be respectively |

| i ➥ 2K, 4K |

| ii ➥ 1024K, 2K |

| iii ➥ 4K, 2048K |

| iv ➥ 2048K, 4K |

| Best Explanation: Answer: (iv) Explanation: Upload Soon |

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.17➡ | NET June 2022 Consider the following related to Fourth Generation Technique (4GT): (A) It controls efforts (B) It controls resources (C) It controls cost of development. Choose the correct answer from the options given below: |

| i ➥ (A) and (B) only |

| ii ➥ (B) and (C) only |

| iii ➥ (C) and (A) only |

| iv ➥ All (A), (B) and (C) |

| Best Explanation: Answer: (iv) Explanation: Upload Soon |

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

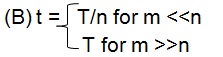

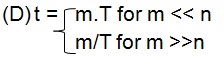

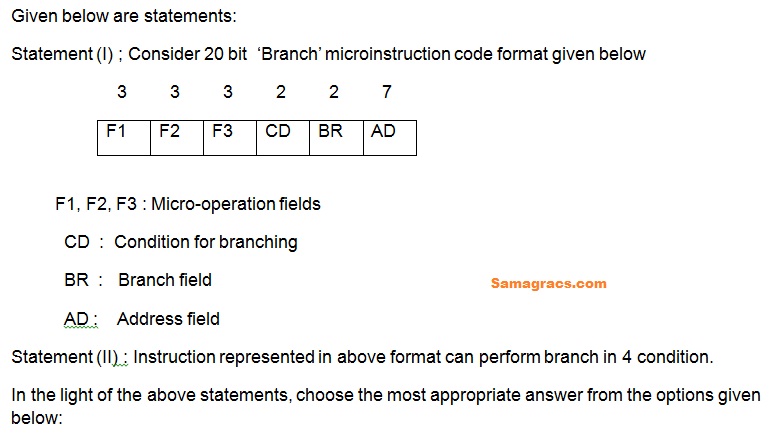

| Q.18➡ | NET June 2022 Consider a memory system having address spaced at a distance of m , T = Bank cycle time and n number of banks , then the average data access time per word access in synchronous organization is |

| i ➥ |

ii ➥  |

iii ➥  |

iv ➥  |

| Best Explanation: Answer: (i) Explanation: Upload Soon |

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.19➡ | NET June 2022 The total storage capacity of a floppy disk having 80 tracks and storing 128 bytes/sector is 163,840 bytes . How many sectors does this disk have ? |

| i ➥ 27 |

| ii ➥ 2048 |

| iii ➥ 4K |

| iv ➥ 16 |

| Best Explanation: Answer: (iv) Explanation: Upload Soon |

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

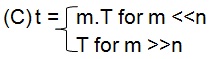

Q.20➡ | NET June 2022 |

| i ➥ Both statement (I) and Statement (II) are correct |

| ii ➥ Both statement (I) and Statement (II) are incorrect |

| iii ➥ Statement (I) is correct and Statement (II) are incorrect |

| iv ➥ Statement (I) is incorrect and Statement (II) are correct |

| Best Explanation: Answer: (i) Explanation: Upload Soon |

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.21➡ | NET June 2022 A 4-stage pipeline has the delay as 150, 120, 160 and 140 ns respectively . registers that are used between the stage have delay of 5 ns. Assuming constant locking rate , the total time required to process 1000 data items on this pipeline is |

| i ➥ 160.5 ns |

| ii ➥ 165.5 ns |

| iii ➥ 120.5 ns |

| iv ➥ 590.5 ns |

| Best Explanation: Answer: (ii) Explanation: Upload Soon |

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.22➡ | NET June 2022 A magnetic tape drive has transport speed of 200 inches per second and a recording density of 1600 bytes per inch. The time required to write 600000 bytes of date grouped in 100 charaters record with a blocking factor 10 is |

| i ➥ 2.0625 sec |

| ii ➥ 2.6251 sec |

| iii ➥ 2.0062 sec |

| iv ➥ 2.6150 sec |

| Best Explanation: Answer: (i) Explanation: Upload Soon |

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.23➡ | NET June 2021 Given below are three statements related to interrupt handling mechanism A. Interrupt handler routine is not stored at a fixed address in the memory. B. CPU hardware has a dedicated wire called the interrupt request line used for handling interrupts C. Interrupt vector contains the memory addresses for speciaized interrupt handlers. In the context of above statements, choose the correct answer from the options given below: Options:- |

| i ➥ A is TRUE only |

| ii ➥ Both A and B are TRUE only |

| iii ➥ Both A, C are TRUE only |

| iv ➥ Both B and C are TRUE only |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.24➡ | NET June 2021 Which of the following statement is true? A. Control memory is part of the hardwired control unit. B. Program control instructions are used to alter the sequential flow of the program. C. The register indirect addressing mode for accessing memory operand is similar to displacement addressing mode. D. CPU utilization is not affected by the introduction of Interrupts. |

| i ➥ A |

| ii ➥ B |

| iii ➥ C |

| iv ➥ D |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.25➡ | NET June 2021 Which of the following is not an example of pseudo-instruction? |

| i ➥ DEC |

| ii ➥ END |

| iii ➥ HLT |

| iv ➥ ORG |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.26➡ | NET June 2021 Given below are two statements Statement I: CISC computers have a large of number of addressing modes. Statement II: In RISC machines memory access is limited to load and store instructions. In light of the above statements, choose the correct answer from the options given below |

| i ➥ Both Statement I and Statement II are false |

| ii ➥ Both Statement I and Statement II are true |

| iii ➥ Statement I is false but Statement II is true |

| iv ➥ Statement I is true but Statement II is false |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.27➡ | NET June 2021 The cache coherence problem can be solved A. by having multiport memory B. allow only nonshared data to be stored in cache C. using a snoopy cache controller D. using memory interleaving Choose the correct answer from the options given below: |

| i ➥ A and C only |

| ii ➥ B and C only |

| iii ➥ B and D only |

| iv ➥ D and C only |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.28➡ | NET June 2021 Arrange the following in the increasing order of complexity. A. I/O Module B. I/O processor C. I/O Channel D. DMA Choose the correct answer from the options given below Options:- |

| i ➥ A, B, C, D |

| ii ➥ A, D, C, B |

| iii ➥ C, D, A, B |

| iv ➥ D, C, B, A |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.29➡ | UGC NET November 2020 Consider a single-level page table system, with the page table stored in the memory. If the hit rate to TLB is 80%, and it takes 15 nanoseconds to search the TLB, and 150 nanoseconds to access the main memory, then what is the effective memory access time, in nanoseconds? |

| i➥ 185 |

| ii ➥ 195 |

| iii ➥ 205 |

| iv ➥ 175 |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

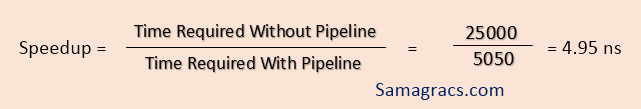

| Q.30➡ | UGC NET November 2020 A non-pipeline system takes 50ns to process a task. The same task can be processed in a six-segment pipeline with a clock cycle of 10ns. Determine approximately the speedup ratio of the pipeline for 500 tasks. |

| i➥ 6 |

| ii ➥ 4.95 |

| iii ➥ 5.7 |

| iv ➥ 5.5 |

| Answer: II Explanation: Given, Total Stage (k) = 6 Time taken by non-pipeline system(Tnp) = 50ns Time taken by pipeline system(Tp) = 10ns Formula, Time required to execute n tasks without pipeline = n*Tnp Time required to execute n tasks with k-stages pipeline = = (k+n-1)*Tp Let’s solve, Time required to execute 500 tasks without pipeline = n*Tnp = 500* 50 = 25000 ns Time required to execute 500 tasks with 6-stages pipeline = Time taken by 1st task + Time taken by remaining 499 tasks = 1 x 6 clock cycles + 499 x 1 clock cycle = 6 clock time + 499 clock time = 6* 10 + 499* 10 = 60 + 4990 = 5050ns or Time required to execute 500 tasks with 6-stages pipeline = (k+n-1)*Tp =(6+500-1)*10 = 505*10 = 5050ns  Therefore, Option(II) is correct. |

| [Easy Solution] | Explanation On YouTube | Learn Topic Wise | Help-Line |

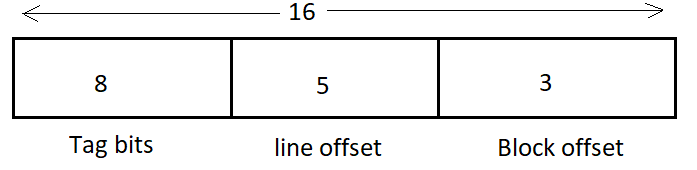

| Q.31➡ | UGC NET November 2020 Consider a machine with a byte addressable main memory of 216 bytes and block size of 8 bytes. Assume that a direct mapped cache consisting of 32 lines is used with this machine. How many bits will be there in Tag, line and word field of format of main memory addresses? |

| i➥ 8,5,3 |

| ii ➥ 8,6,2 |

| iii ➥ 7,5,4 |

| iv ➥ 7,6,3 |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.32➡ | UGC NET November 2020 Given below are two statements: Statement I: hardwired control unit can be optimized to produce fast mode of operation. Statement II: Indirect addressing mode needs two memory references to fetch the operand. In the light of the above statements, choose the correct answers from the options given below |

| i➥ Both Statement I and Statement II are true |

| ii ➥ Both Statement I and Statement II are false |

| iii ➥ Statement I is correct but Statement II is false |

| iv ➥ Statement I is incorrect but Statement II is true |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

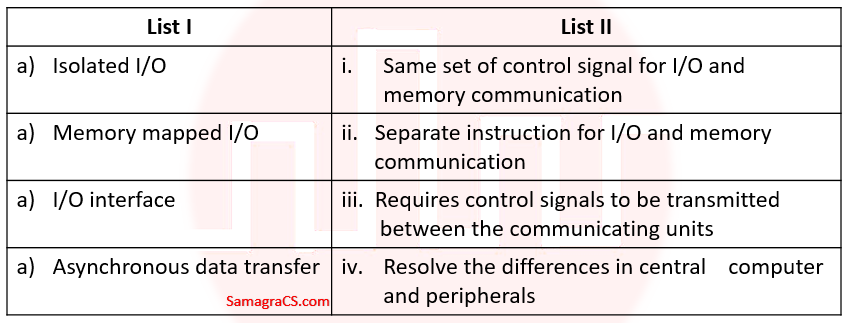

| Q.33➡ | UGC NET November 2020 Match list I and List II  Choose the correct answer from the options given below: |

| i➥ A-I, B-II, C-III, D-IV |

| ii ➥ A-II, B-IV, C-III, D-I |

| iii ➥ A-II, B-IV, C-I, D-III |

| iv ➥ A-IV, B-III, C-II, D-I |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.34➡ | UGC NET November 2020 Arrange the following types of machine in descending order of complexity. (A) SISD (B) MIMD (C) SIMD Choose the correct answer from the options given below: |

| i➥ A, B, C |

| ii ➥ C, B, A |

| iii ➥ B, C, A |

| iv ➥ C, A, B |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.35➡ | UGC NET November 2020 Which of the following statements with respect to K-segment pipelining are true? A) Maximum speedup that a pipeline can provide is k theoretically. B) It is impossible to achieve maximum speedup k in the k-segment pipeline. C) All segments in the pipeline take the same time in computation. Choose the correct answer from the options given below: |

| i➥ (A) and (B) only |

| ii ➥ (B) and (C) only |

| iii ➥ (A) and (C) only |

| iv ➥ (A), (B) and (C) |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

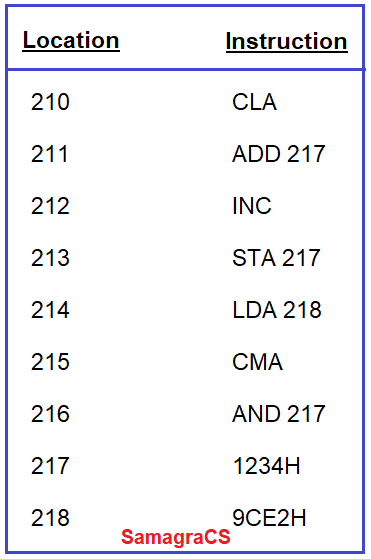

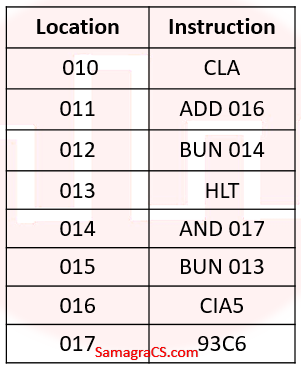

| Q.36➡ | UGC NET November 2020 The following program is stored in the memory unit of the basic computer. What is the content of the accumulator after the execution of the program? (All location numbers listed below are in hexadecimal)  |

| i➥ 1002H |

| ii ➥ 2011H |

| iii ➥ 2022H |

| iv ➥ 0215H |

| Answer: IV |

| [Easy Solution] | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.37➡ | UGC NET November 2020 The period of a signal is 100ms. then the frequency of this signal in kilohertz is __? |

| i➥ 10 |

| ii ➥ 10-1 |

| iii ➥ 10-2 |

| iv ➥ 10-3 |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.38➡ | NTA UGC NET November 2020 Comprehension: Question 16-20 concerns a disk with a sector size of 512 bytes, 2000 tracks per surface.50 sectors per track, five double-sided platters, and average seek time of 10 milliseconds. Q16: If one track of data can be transferred per revolution, then what is the data transfer rate? |

| i➥ 2,850 KBytes/second |

| ii ➥ 4,500 KBytes/second |

| iii ➥ 5,700 KBytes/second |

| iv ➥ 2,250 KBytes/second |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.39➡ | NTA UGC NET November 2020 Comprehension: Question 16-20 concerns a disk with a sector size of 512 bytes, 2000 tracks per surface.50 sectors per track, five double-sided platters, and average seek time of 10 milliseconds. Q17: Given below are two statements: Statement I: The disk has a total number of 2000 cylinders. Statement II: 51200 bytes is not a valid block size for the disk. In the light of the above statements, choose the correct answer from the options given below: |

| i➥ Both Statement I and Statement II are true |

| ii ➥ Both Statement I and Statement II are false |

| iii ➥ Statement I is correct but Statement II is false |

| iv ➥ Statement I is incorrect but Statement II is true |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.40➡ | NTA UGC NET November 2020 Comprehension: Question 16-20 concerns a disk with a sector size of 512 bytes, 2000 tracks per surface.50 sectors per track, five double-sided platters, and average seek time of 10 milliseconds. Q18: If T is the capacity of a track in bytes, and S is the capacity of each surface in bytes, then (T,S) = __________. |

| i➥ (50 K, 50000 K) |

| ii ➥ (50 K, 50000 K) |

| iii ➥ (25 K, 50000 K) |

| iv ➥ (40 K, 36000 K) |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.41➡ | NTA UGC NET November 2020 Comprehension: Question 16-20 concerns a disk with a sector size of 512 bytes, 2000 tracks per surface.50 sectors per track, five double-sided platters, and average seek time of 10 milliseconds. Q19: What is the capacity of the disk, in bytes? |

| i➥ 25,000 K |

| ii ➥ 500,000 K |

| iii ➥ 250,000 K |

| iv ➥ 50,000 K |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.42➡ | UGC NET November 2020 Comprehension: Question 16-20 concerns a disk with a sector size of 512 bytes, 2000 tracks per surface.50 sectors per track, five double-sided platters, and average seek time of 10 milliseconds. Q20: If the disk platters rotate at 5400 rpm (revolutions per minute), then approximately what is the maximum rotational delay? |

| i➥ 0.011 seconds |

| ii ➥ 0.11 seconds |

| iii ➥ 0.0011 seconds |

| iv ➥ 1.1 seconds |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.43➡ | UGC NET December 2019 A Non-pipelined system takes 30ns to process a task. The same task can be processed in a four-segment pipeline with a clock cycle of 10ns. Determine the speed up of the pipeline for 100 tasks |

| i➥ 3 |

| ii ➥ 4 |

| iii ➥ 3.91 |

| iv ➥ 2.91 |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.44➡ | UGC NET December 2019 The reduced Instruction Set Computer (RISC) characteristics are: (a) Single cycle instruction execution (b) Variable length instruction formats (c) Instructions that manipulates operands in memory (d) Efficient instruction pipeline Choose the correct characteristics from the options given below: |

| i➥ (a) and (b) |

| ii ➥ (b) and (c) |

| iii ➥ (a) and (d) |

| iv ➥ (c) and (d) |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

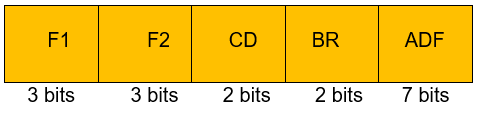

| Q.45➡ | UGC NET December 2019 A micro instruction format has micro operation field which is divided into 2 sub fields F1 and F2. Each having 15 distinct micro operations condition field CD for four status bits. Branch field BR having four options used in conjunction with address field AD. The address space is of 128 memory words. The size of micro instruction is |

| i➥ 19 |

| ii ➥ 18 |

| iii ➥ 17 |

| iv ➥ 20 |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.46➡ | UGC NET December 2019 Consider a paging system where translation lookaside buffer (TLB) a special type of associative memory is used with hit ratio of 80%. Assume that memory reference takes 80 nanoseconds and reference time to TLB is 20 nanoseconds. What will be the effective memory access time given 80% hit ratio? |

| i➥ 110 nanoseconds |

| ii ➥ 116 nanoseconds |

| iii ➥ 200 nanoseconds |

| iv ➥ 100 nanoseconds |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.47➡ | UGC NET December 2019 A computer uses a memory unit of 512 K words of 32 bits each. A binary instruction code is stored in one word of the memory. The instruction has four parts: an addressing mode field to specify one of the two-addressing mode (direct and indirect), an operation code, a register code part to specify one of the 256 registers and an address part. How many bits are there in addressing mode part, opcode part, register code part and the address part? |

| i ➥ 1, 3, 9, 19 |

| ii ➥ 1, 4, 9, 18 |

| iii ➥ 1, 4, 8, 19 |

| iv ➥ 1, 8, 8, 20 |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.48➡ | UGC NET December 2019 Match List-I and List-II:  Choose the correct option from those given below: |

| i ➥ (a)-(ii), (b)-(iii), (c)-(iv), (d)-(i) |

| ii ➥ (a)-(i), (b)-(ii), (c)-(iii), (d)-(iv) |

| iii ➥ (a)-(ii), (b)-(i), (c)-(iv), (d)-(iii) |

| iv ➥ (a)-(i), (b)-(ii), (c)-(iv), (d)-(iii) |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

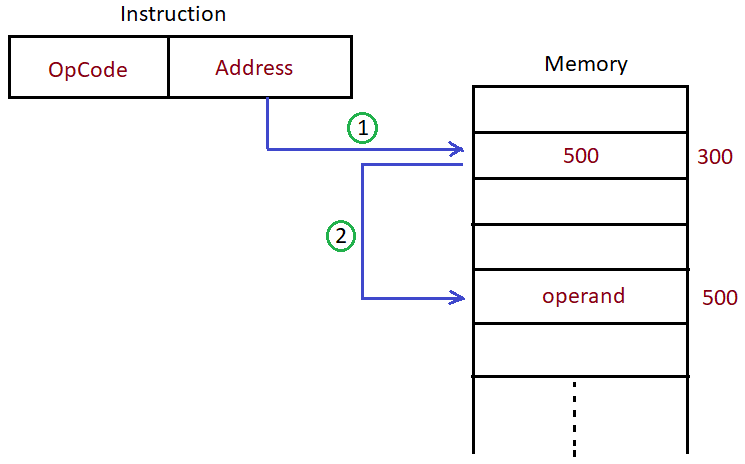

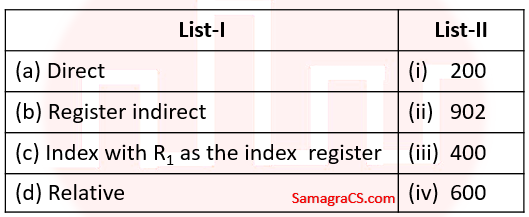

| Q.49➡ | UGC NET December 2019 An instruction is stored at location 500 with it address field at location 501. The address field has the value 400. A processor register R1 contains the number 200. Match the addressing mode (List-I) given below with effective address (List-II) for the given instruction:  Choose the correct option from those given below: |

| i ➥ (a)-(iii), (b)-(i), (c)-(iv), (d)-(ii) |

| ii ➥ (a)-(i), (b)-(ii), (c)-(iii), (d)-(iv) |

| iii ➥ (a)-(iv), (b)-(ii), (c)-(iii), (d)-(i) |

| iv ➥ (a)-(iv), (b)-(iii), (c)-(ii), (d)-(i) |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

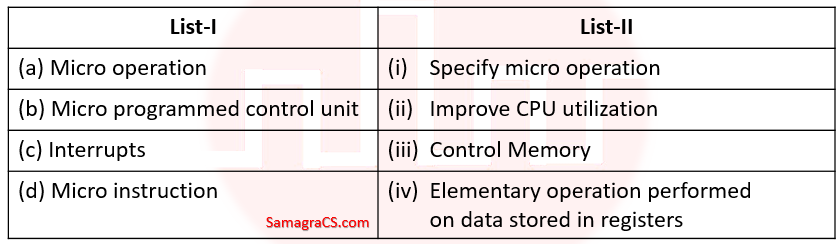

| Q.50➡ | UGC NET December 2019 Match List-I and List-II:  Choose the correct option from those given below: |

| i ➥ (a)-(iv), (b)-(iii), (c)-(ii), (d)-(i) |

| ii ➥ (a)-(iv), (b).(iii), (c)-(i), (d)-(ii) |

| iii ➥ (a)-(iii), (b)-(iv), (c)-(i), (d)-(i) |

| iv ➥ (a)-(iii), (b)-(iv), (c)-(ii), (d)-(i) |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.51➡ | UGC NET December 2019 The following program is stored in the memory unit of the basic computer. Give the content of accumulator register in hexadecimal after the execution of the program.  |

| i ➥ A1B4 |

| ii ➥ 81B4 |

| iii ➥ A184 |

| iv ➥ 8184 |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.52➡ | UGC NET June 2019 Which type of addressing mode, less number of memory references are required? |

| i ➥ Immediate |

| ii ➥ Implied |

| iii ➥ register |

| iv ➥ indexed |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.53➡ | UGC NET June 2019 Suppose that the register A and register K have the bit configuration. Only the three leftmost bits of A are compared with memory words because K has 1’s in these positions. Because of its organization, this type of memory is uniquely suited to parallel searches by data association. This type of memory is known as |

| i ➥ RAM |

| ii ➥ ROM |

| iii ➥ Content addressable memory |

| iv ➥ Secondary memory |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.54➡ | UGC NET June 2019 For a magnetic disk with concentric circular tracks, the seek latency is not linearly proportional to the seek distance due to |

| i ➥ Non-Uniform distribution of requests |

| ii ➥ arm starting or stopping inertia |

| iii ➥ higher capacity of tracks on the periphery of the plate |

| iv ➥ use of unfair arm scheduling policies |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.55➡ | UGC NET June 2019 The fault can be easily diagnosed in the micro-program control unit using diagnostic tools by maintaining the contents of. |

| i ➥ Flags and Counters |

| ii ➥ Registers and counters |

| iii ➥ Flags and registers |

| iv ➥ Flags, registers and counters |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.56➡ | UGC NET June 2019 Suppose that a computer program takes 100 seconds of execution time on a computer with multiplication operation responsible for 80 seconds of this time. How much do you have to improve the speed of multiplication operation if you are asked to execute this program four times faster. |

| i ➥ 14 times faster |

| ii ➥ 15 times faster |

| iii ➥ 16 times faster |

| iv ➥ 17 times faster |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.57➡ | UGC NET December 2018 Consider a disk pack with 32 surfaces, 64 tracks and 512 sectors per pack. 256 bytes of data are stored in a bit serial manner in a sector. The number of bits required to specify a particular sector in the disk is. |

| i ➥ 19 |

| ii ➥ 20 |

| iii ➥ 18 |

| iv ➥ 22 |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.58➡ | UGC NET December 2018 Dirty bit is used to show the |

| i ➥ Page with low frequency occurrence |

| ii ➥ Wrong page |

| iii ➥ Page with corrupted data |

| iv ➥ Page that is modified after being loaded into cache memory |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.59➡ | UGC NET December 2018 Consider the following x86 – assembly language instructions : MOV AL, 153 NEG AL The contents of the destination register AL (in 8-bit binary notation), the status of Carry Flag(CF) and Sign Flag(SF) after the execution of above instructions, are |

| i ➥ AL = 0110 0110; CF = 0; SF =0 |

| ii ➥ AL = 0110 0111; CF = 0; SF =1 |

| iii ➥ AL = 0110 0110; CF = 1; SF =1 |

| iv ➥ AL = 0110 0111; CF = 1; SF =0 |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.60➡ | UGC NET December 2018 Consider the following statements : (i) Auto increment addressing mode is useful in creating self-relocating code. (ii) If auto addressing mode is included in an instruction set architecture, then an additional ALU is required for effective address calculation. (iii) In auto increment addressing mode, the amount of increment depends on the size of the data item accessed. Which of the above statements is/are true ? |

| i ➥ (iii) only |

| ii ➥ (ii) and (iii) only |

| iii ➥ (i) and (ii) only |

| iv ➥ (ii) only |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.61➡ | UGC NET June 2018 Normally user programs are prevented from handling I/O directly by I/O instructions in them. For CPUs having explicit I/O instructions, such I/O protection is ensured by having the I/O instructions privileged. In a CPU with memory mapped I/O, there is no explicit I/O instruction. Which one of the following is true for a CPU with memory mapped I/O ? |

| i ➥ I/O protection is ensured by operating system routines. |

| ii ➥ I/O protection is ensured by a hardware trap. |

| iii ➥ I/O protection is ensured during system configuration. |

| iv ➥ I/O protection is not possible. |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.62➡ | UGC NET June 2018 Which of the following mapping is not used for mapping process in cache memory? |

| i ➥ Associative mapping |

| ii ➥ Direct mapping |

| iii ➥ Set-Associative mapping |

| iv ➥ Segmented – page mapping |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.63➡ | UGC NET June 2018 In 8085 microprocessor, what is the output of following program ? LDA 8000H MVI B, 30H ADD B STA 8001H |

| i ➥ Read a number from input port and store it in memory |

| ii ➥ Read a number from input device with address 8000H and store it in memory at location 8001H |

| iii ➥ Read a number from memory at location 8000H and store it in memory location 8001H |

| iv ➥ Load A with data from input device with address 8000H and display it on the output device with address 8001H |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.64➡ | UGC NET November 2017 Paper-3 In 8085 microprocessor which of the following flag(s) is (are) affected by an arithmetic operation? |

| i ➥ AC flag Only |

| ii ➥ CY flag Only |

| iii ➥ Z flag Only |

| iv ➥ AC, CY, Z flags |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.65➡ | UGC NET November 2017 Paper-3 In 8085 microprocessor the address bus is of________bits. |

| i ➥ 4 |

| ii ➥ 8 |

| iii ➥ 16 |

| iv ➥ 32 |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.66➡ | UGC NET November 2017 Paper-3 In the architecture of 8085 microprocessor match the following:  Code: |

| i ➥ (a)-(iv), (b)-(i), (c)-(ii) |

| ii ➥ (a)-(iii), (b)-(iv), (c)-(ii) |

| iii ➥ (a)-(ii), (b)-(iii), (c)-(i) |

| iv ➥ (a)-(i), (b)-(ii), (c)-(iv) |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.67➡ | UGC NET November 2017 Paper-3 Which of the following addressing mode is best suited to access elements of an array of contiguous memory locations ? |

| i ➥ Indexed addressing mode |

| ii ➥ Base Register addressing mode |

| iii ➥ Relative address mode |

| iv ➥ Displacement mode |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.68➡ | UGC NET November 2017 Paper-3 Which of the following is correct statement ? |

| i ➥ In memory – mapped I/O, the CPU can manipulate I/O data residing in interface registers that are not used to manipulate memory words. |

| ii ➥ The isolated I/O method isolates memory and I/O addresses so that memory address range is not affected by interface address assignment. |

| iii ➥ In asynchronous serial transfer of data the two units share a common clock. |

| iv ➥ In synchronous serial transmission of data the two units have different clocks. |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.69➡ | UGC NET November 2017 Paper-3 A micro-instruction format has micro-ops field which is divided into three sub-fields F1, F2, F3 each having seven distinct micro-operations, condition field CD for four status bits, branch field BR having four options used in conjunction with address field ADF. The address space is of 128 memory locations. The size of micro-instruction is: |

| i ➥ 17 |

| ii ➥ 20 |

| iii ➥ 24 |

| iv ➥ 32 |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.70➡ | UGC NET November 2017 Paper-3 Consider the following assembly program fragment : stc mov al, 11010110b mov cl, 2 rcl al, 3 rol al, 4 shr al, cl mul cl The contents of the destination register ax (in hexadecimal) and the status of Carry Flag (CF) after the execution of above instructions, are: |

| i ➥ ax=003CH; CF=0 |

| ii ➥ ax=001EH; CF=0 |

| iii ➥ ax=007BH; CF=1 |

| iv ➥ ax=00B7H; CF=1 |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.71➡ | UGC NET January 2017 Paper-3 Which of the following is an interrupt according to temporal relationship with system clock? |

| i ➥ Maskable interrupt |

| ii ➥ Periodic interrupt |

| iii ➥ Division by zero |

| iv ➥ Synchronous interrupt |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

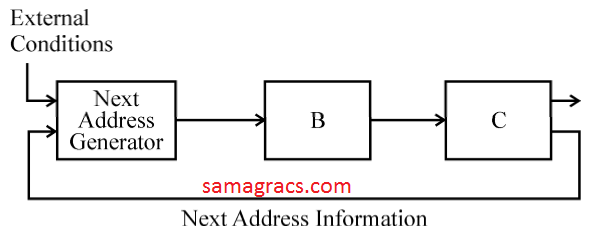

| Q.72➡ | UGC NET January 2017 Paper-3 The general configuration of the micro-programmed control unit is given below:  What are blocks B and C in the diagram respectively? |

| i ➥ Block address register and cache memory |

| ii ➥ Control address register and control memory |

| iii ➥ Branch register and cache memory |

| iv ➥ Control address register and random access |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

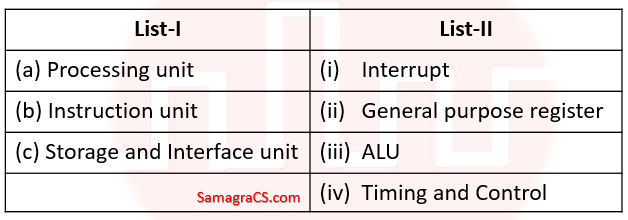

| Q.73➡ | UGC NET January 2017 Paper-3 Match the following :  |

| i ➥ a-(iv), b-(iii), c-(i), d-(ii) |

| ii ➥ a-(iv), b-(i), c-(iii), d-(ii) |

| iii ➥ a-(iv), b-(ii), c-(i), d-(iii) |

| iv ➥ a-(iv), b-(iii), c-(ii), d-(i) |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.74➡ | UGC NET January 2017 Paper-3 In 8085 microprocessor, the digit 5 indicates that the microprocessor needs: |

| i ➥ –5 volts, +5 volts supply |

| ii ➥ +5 volts supply only |

| iii ➥ –5 volts supply only |

| iv ➥ 5 MHz clock |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

| Q.75➡ | UGC NET January 2017 Paper-3 In 8085, which of the following performs : load register pair immediate operation? |

| i ➥ LDAX rp |

| ii ➥ LHLD addr |

| iii ➥ LXI rp, data |

| iv ➥ INX rp |

Show Answer With Best Explanation

| More Discussion | Explanation On YouTube | Learn Topic Wise | Help-Line |

NTA UGC NET Subject Wise Previous Year Question With Solutions