GATE/NET Digital Logic Design Practice Test Set7

Q6➡ |

The number of control lines for a 8 to 1 multiplexer is |

Q7➡ |

The number of full and half adders required to add 16-bit numbers are |

| i ➥ 8 half adders, 8 full adders |

| ii ➥ 1 half adder, 15 full adders |

| iii ➥ 16 half adders, 0 full adders |

| iv ➥ 1 half adders, 12 full adders |

Q8➡ |

How many 64Kx1RAM chips are required to provide a memory of size 256K bytes? |

| i ➥ 8 |

| ii ➥ 4 |

| iii ➥ 32 |

| iv ➥ 64 |

Q9➡ |

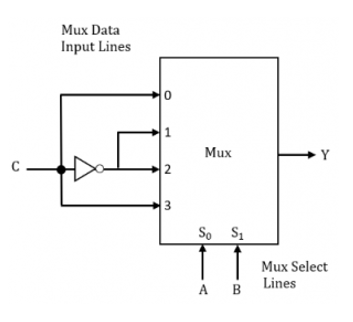

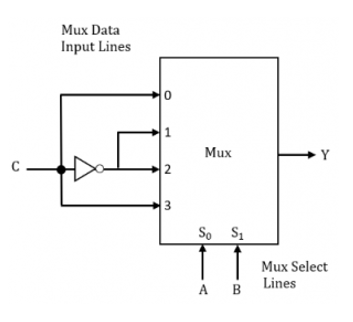

Following Multiplexer circuits is equivalent to

|

| i ➥ Sum equation of full adder |

| ii ➥ Carry equation of full adder |

| iii ➥ Difference equation of a full subtractor |

| iv ➥ Both I and III |

Q10➡ |

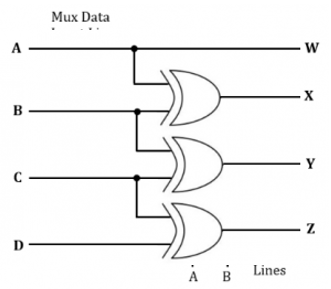

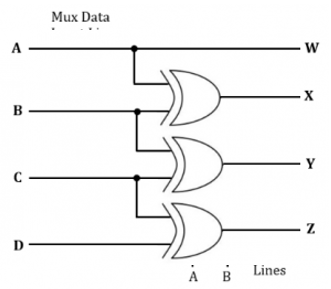

If ABCD is a 4-bit binary number, then what is code generated by the following circuit?

|

| i ➥ BCD code |

| ii ➥ Gray code |

| iii ➥ 8421 code |

| iv ➥ Excess-3 code |

6-ii

7-ii

9-i

6, ii

7, ii

8, ii

9, ii

10, i .

Ans6-ii

Ans7-ii

Ans8-i

Ans9-i

Ans10-iii

Ans 6 – 3

Ans 7- 1

Ans 8 – 4

Ans 9 – 4

Ans 10 – 3

6.ii

7.ii

8……

9…..

10.i